# **FXPS7550D4S**

## Digital absolute pressure sensor, 20 kPa to 550 kPa

Rev. 1.3 — 3 November 2023

Product data sheet

## 1 General description

The FXPS7550D4S high-performance, high-precision barometric absolute pressure (BAP) sensor consists of a compact capacitive micro-electro-mechanical systems (MEMS) device coupled with a digital integrated circuit (IC) producing a fully calibrated digital output.

The sensor is based on NXP's high-precision capacitive pressure cell technology. The architecture benefits from redundant pressure transducers as an expanded quality measure. This sensor delivers highly accurate pressure and temperature readings through either a serial peripheral interface (SPI) or an inter-integrated circuit (I<sup>2</sup>C) interface. Furthermore, the sensor employs an on-demand digital self-test for the digital IC and the MEMS transducers.

The sensor operates over a pressure range of 20 kPa to 550 kPa and over a wide temperature range of −40 °C to 130 °C.

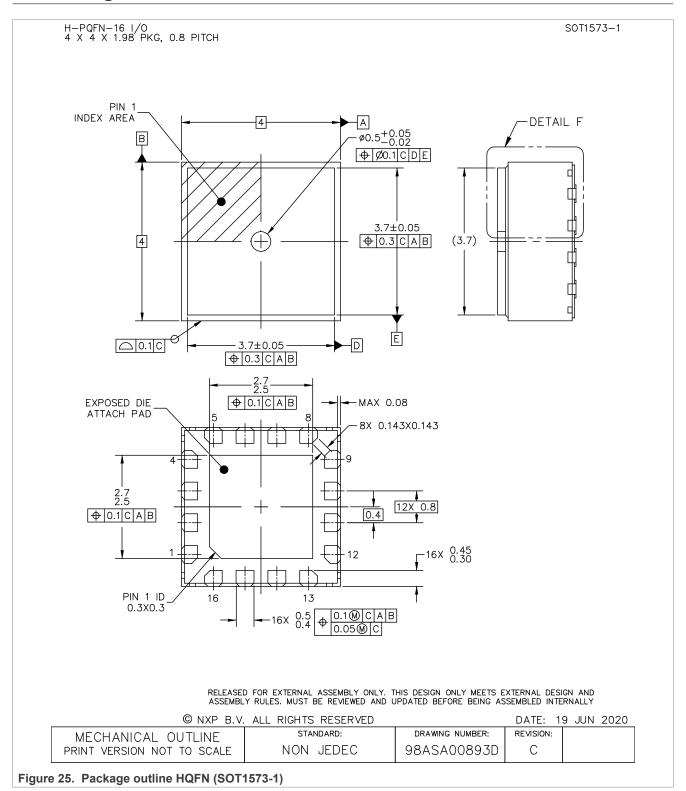

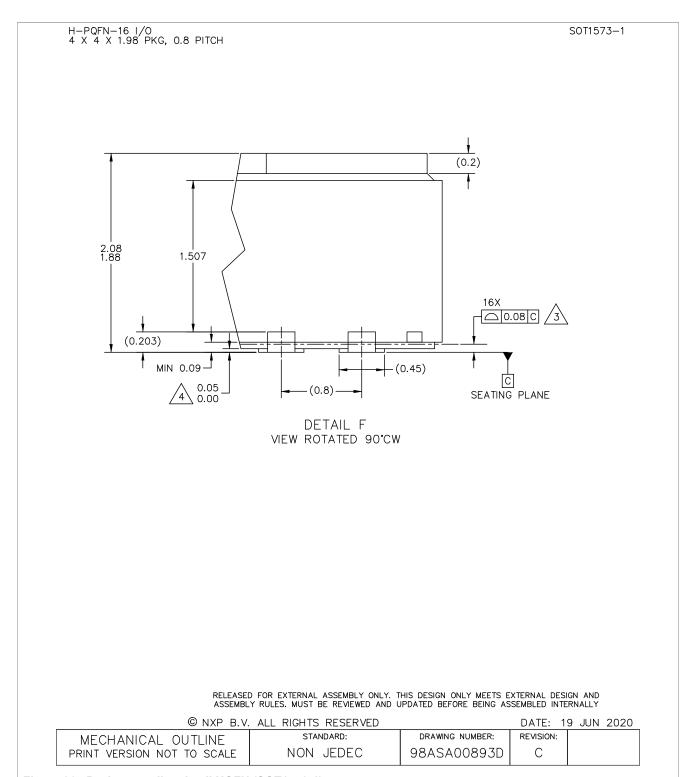

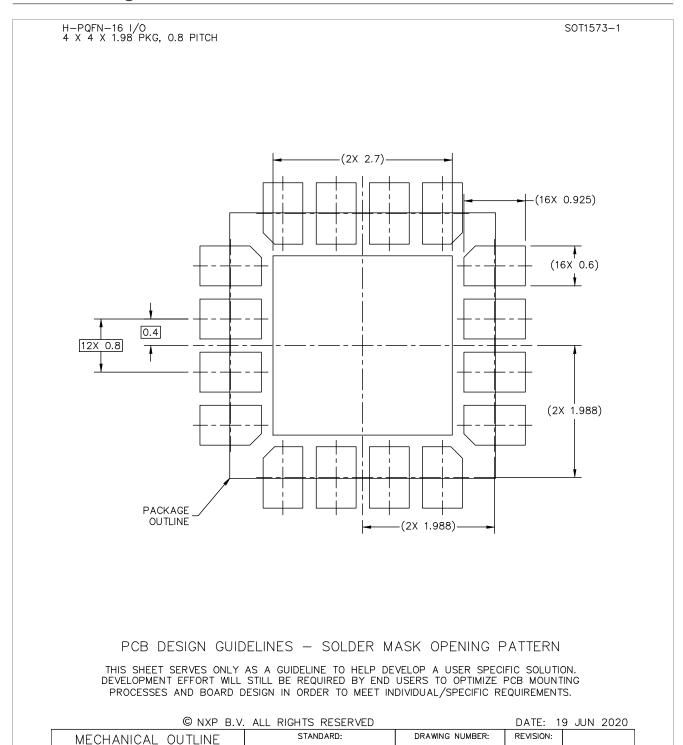

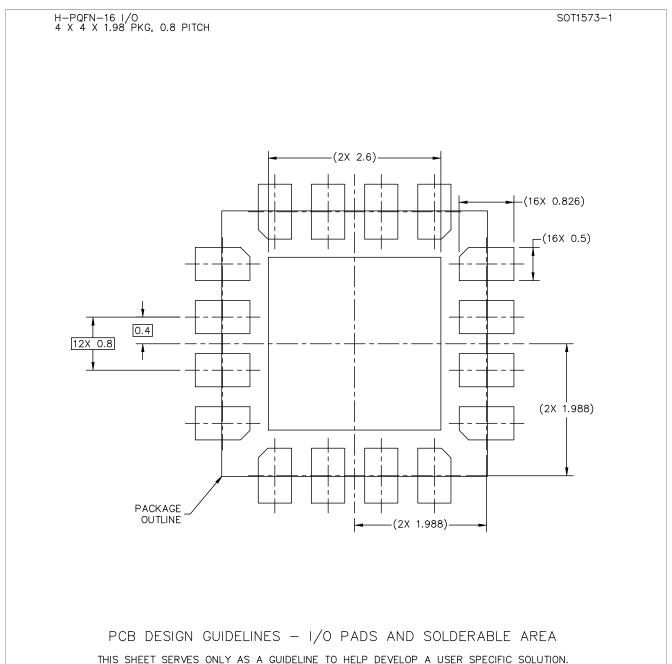

The sensor comes in an industry-leading 4 mm x 4 mm x 1.98 mm, restriction of hazardous substances (RoHS) compliant, high power quad flat no lead (HQFN) package<sup>[1]</sup> suitable for small PCB integration. Its AEC-Q100<sup>[2]</sup> compliance, high accuracy, reliable performance, and high media resistivity make it ideal for use in automotive, industrial, and consumer applications.

## 2 Features and benefits

- Absolute pressure range: 20 kPa to 550 kPa

- Operating temperature range: -40 °C to 130 °C

- Pressure transducer and digital signal processor (DSP)

- Digital self-test

- I<sup>2</sup>C compatible serial interface

- Client mode operation

- Standard mode, Fast mode, and Fast-mode Plus support

- 32-bit SPI compatible serial interface

- Sensor data transmission commands

- 12-bit data for absolute pressure

- 8-bit data for temperature

- 2-bit basic status and 2-bit detailed status fields

- 3, 4, or 8-bit configurable CRC

- · Capacitance to voltage converter with anti-aliasing filter

- Sigma delta ADC plus sinc filter

- 800 Hz or 1000 Hz low-pass filter for absolute pressure

- Lead-free, 16-pin HQFN, 4 mm x 4 mm x 1.98 mm package

# 3 Applications

#### 3.1 Automotive

- · Engine management digital MAP and BAP

- Small engine control

- · Liquid propane gas (LPG) or compressed natural gas (CNG) engine management

#### 3.2 Industrial

- · Compressed air

- · Manufacturing line control

- · Gas metering

- · Weather stations

## 3.3 Medical/Consumer

- · Blood pressure monitor

- · Medicine dispensing systems

- · White goods

# 4 Ordering information

## Table 1. Ordering information

| Type number                  | Package |                                                                                                                    |           |

|------------------------------|---------|--------------------------------------------------------------------------------------------------------------------|-----------|

|                              | Name    | Description                                                                                                        | Version   |

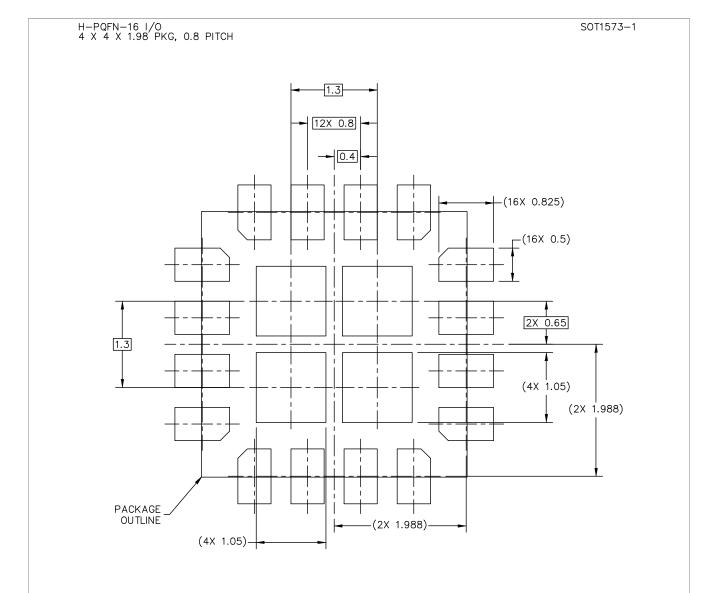

| FXPS7550DI4S<br>FXPS7550DS4S |         | HQFN16, plastic, thermal enhanced quad flat pack; no leads; 16 terminals; 0.8 mm pitch; 4 mm x 4 mm x 1.98 mm body | SOT1573-1 |

## 4.1 Ordering options

#### Table 2. Ordering options

| Device                        | Range [kPa]       | Packing       | Interface        | Temperature range |

|-------------------------------|-------------------|---------------|------------------|-------------------|

| FXPS7550DI4ST1 <sup>[1]</sup> | 20 kPa to 550 kPa | Tape and reel | I <sup>2</sup> C | -40 °C to 130 °C  |

| FXPS7550DS4ST1 <sup>[1]</sup> | 20 kPa to 550 kPa | Tape and reel | SPI              | –40 °C to 130 °C  |

<sup>[1]</sup> Product under development, consult your NXP sales representatives for samples.

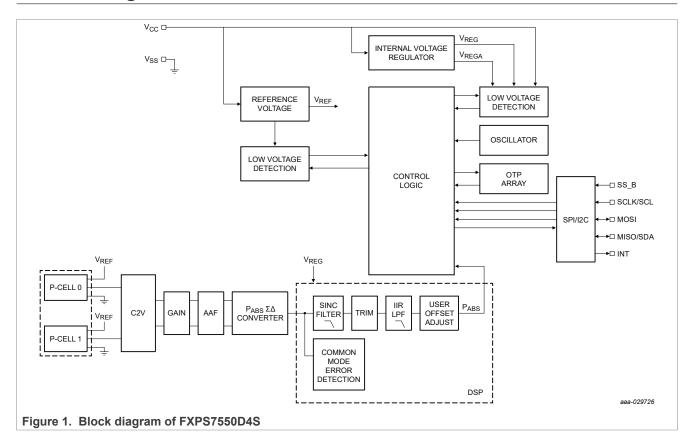

# 5 Block diagram

# 6 Pinning information

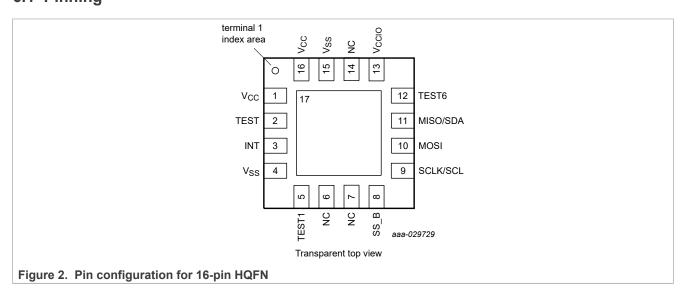

## 6.1 Pinning

## 6.2 Pin description

Table 3. Pin description

| Pin      | Pin name          | Description                                                                                                                                                                                                                                                                                          |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | INT               | Interrupt output  The output can be configured to be active low or active high. If unused, NXP recommends pin 3 be unterminated. Optionally, pin 3 can be tied to V <sub>SS</sub> .                                                                                                                  |

| 1, 16    | V <sub>CC</sub>   | Power supply                                                                                                                                                                                                                                                                                         |

| 4, 15    | V <sub>SS</sub>   | Supply return (ground)                                                                                                                                                                                                                                                                               |

| 2, 12    | TESTx             | Test pin. NXP recommends pins 2, and 12 be unterminated. Optionally, these pins can be tied to V <sub>SS</sub> .                                                                                                                                                                                     |

| 5        | TESTx             | Test pin. NXP recommends pin 5 be tied to V <sub>CC</sub> . Optionally, this pin can be tied to V <sub>SS</sub> . This pin should <b>not</b> be left unconnected.                                                                                                                                    |

| 6, 7, 14 | NC                | No connect                                                                                                                                                                                                                                                                                           |

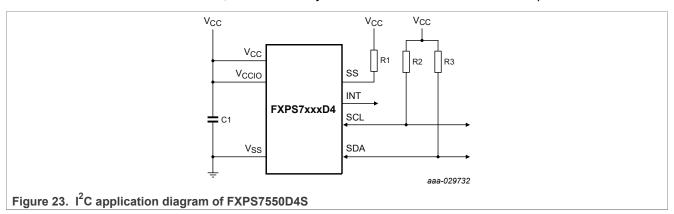

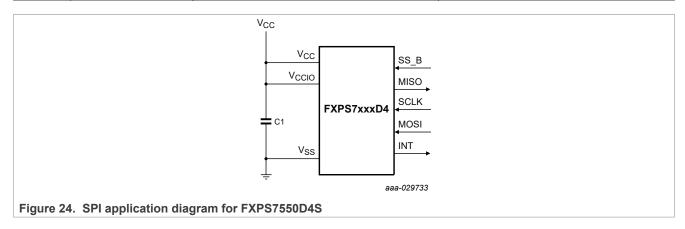

| 8        | SS_B              | Client / Device select In I <sup>2</sup> C mode, input pin 8 must be connected to V <sub>CC</sub> with an external pull-up resistor, as shown in the application diagram. In SPI mode, input pin 8 provides the client select for the SPI port. An internal pull-up device is connected to this pin. |

| 9        | SCLK/SCL          | In I <sup>2</sup> C mode, input pin 9 provides the serial clock. This pin must be connected to V <sub>CC</sub> with an external pull-up resistor, as shown in the application diagram.  In SPI mode, input pin 9 provides the serial clock. An internal pull-down device is connected to this pin.   |

| 10       | MOSI              | SPI data in In SPI mode, pin 10 functions as the serial data input to the SPI port. An internal pull-down device is connected to this pin.                                                                                                                                                           |

| 11       | MISO/SDA          | SPI/I <sup>2</sup> C data out In I <sup>2</sup> C mode, pin 11 functions as the serial data input/output. Pin 11 must be connected to V <sub>CC</sub> with an external pull-up resistor, as shown in the application diagram. In SPI mode, pin 11 functions as the serial data output.               |

| 13       | V <sub>CCIO</sub> | I/O supply Pin 13 must be connected to $V_{\text{CC}}$ , the device supply.                                                                                                                                                                                                                          |

| 17       | PAD               | Die attach pad Pin 17 is the die attach flag, and must be connected to $V_{\text{SS}}$ .                                                                                                                                                                                                             |

# 7 Functional description

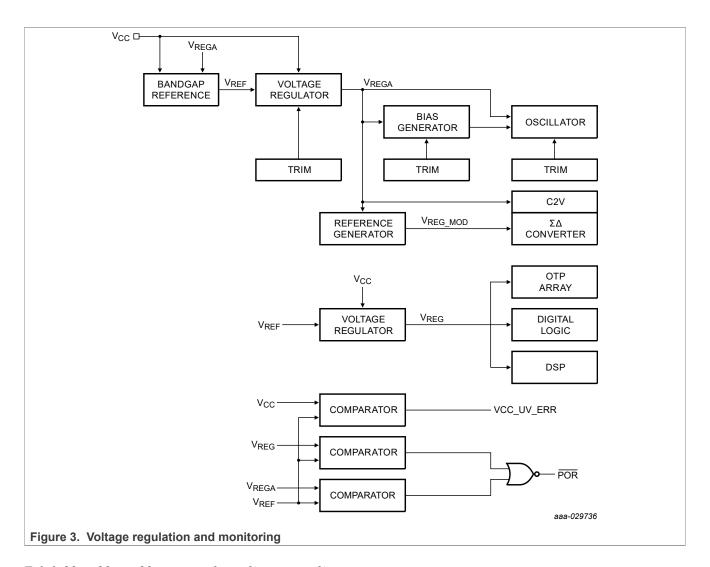

## 7.1 Voltage regulators

The device derives its internal supply voltage from the  $V_{CC}$  and  $V_{SS}$  pins. An external filter capacitor is required for  $V_{CC}$ , as shown in Figure 23 and Figure 24.

A reference generator provides a reference voltage for the  $\Sigma\Delta$  converter.

## 7.1.1 V<sub>CC</sub>, V<sub>REG</sub>, V<sub>REGA</sub>, undervoltage monitor

A circuit is incorporated to monitor the  $V_{CC}$  supply voltage and the internally regulated voltages  $V_{REG}$  and  $V_{REGA}$ . If any of the voltages fall below the specified undervoltage thresholds in <u>Table 104</u>, SPI and I<sup>2</sup>C transactions are terminated. Once the supply returns above the threshold, the device resumes responses.

#### 7.2 Internal oscillator

The device includes a factory trimmed oscillator.

## 7.3 Pressure sensor signal path

#### 7.3.1 Self-test functions

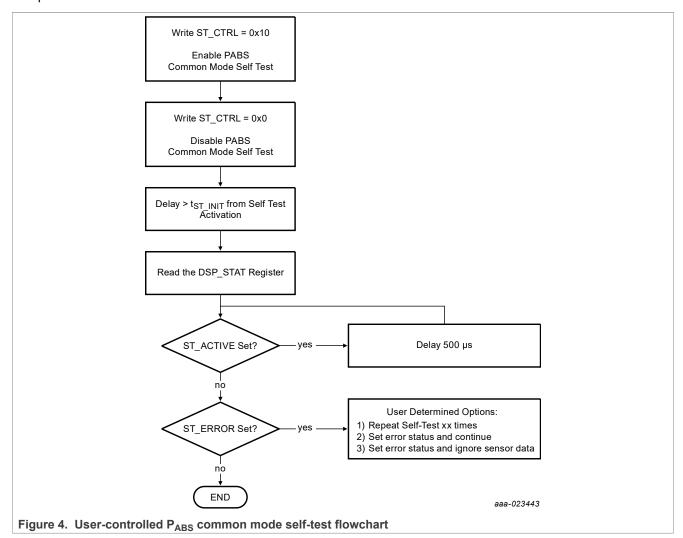

The device includes analog and digital self-test functions to verify the functionality of the transducer and the signal chain. The self-test functions are selected by writing to the ST\_CTRL[3:0] bits in the DSP\_CFG\_U5 register. The ST\_CTRL bits select the desired self-test connection.

Once the ENDINIT bit is set, the ST\_CTRL bits are forced to '0000'. Future writes to the ST\_CTRL bits are disabled until a device reset.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

## 7.3.1.1 P<sub>ABS</sub> common mode verification

When the  $P_{ABS}$  common mode self-test is selected, the ST\_ACTIVE bit is set, the ST\_ERROR is cleared, and the device begins an internal measurement of the common mode signal of the P-cells and compares the result against a predetermined limit. If the result exceeds the limit, the ST\_ERROR bit is set. The  $P_{ABS}$  common mode self-test repeats continuously every  $t_{ST\_INIT}$  when the ST\_CTRL bits are set to the specified value. Once the test is disabled, the ST\_ERROR bit updates with the final test result within  $t_{ST\_INIT}$  of disabling the test. The ST\_ACTIVE bit remains set until the final test result is reported. Figure 4 is an example of a user-controlled self-test procedure.

#### 7.3.1.2 Startup digital self-test verification

Four unique fixed values can be forced at the output of the sinc filter by writing to the ST\_CTRL bits as shown in Table 4. The digital self-test values result in a constant value at the output of the signal chain. After a specified time period, the SNS\_DATAx register value can be verified against the specified values in the table below. The values listed below are for the P<sub>ABS</sub> signal. When any of these self-test functions are selected, the ST\_ACTIVE bit is set. These signals can only be selected when the ENDINIT bit is not set.

Table 4. Self-test control register

| _ |            |            |            |            |                      |                             |

|---|------------|------------|------------|------------|----------------------|-----------------------------|

|   | ST_CTRL[3] | ST_CTRL[2] | ST_CTRL[1] | ST_CTRL[0] | Function             | SNS_DATAx register contents |

|   | 1          | 1          | 0          | 0          | Digital self-test #1 | 8171h                       |

| Ī | 1          | 1          | 0          | 1          | Digital self-test #2 | 6C95h                       |

|   | 1          | 1          | 1          | 0          | Digital self-test #3 | 807Ah                       |

| Ī | 1          | 1          | 1          | 1          | Digital self-test #4 | 78ACh                       |

### 7.3.1.3 Startup sense data fixed value verification

Four unique fixed values can be forced to the SNS\_DATAX\_x registers by writing to the ST\_CTRL bits as shown in <u>Table 5</u>. When any of these values are selected, the ST\_ACTIVE bit is set. These signals can only be selected when the ENDINIT bit is not set.

Table 5. Self-test control bits for sense data fixed value verification

| ST_CTRL[3] | ST_CTRL[2] | ST_CTRL[1] | ST_CTRL[0] | Function                                          | SNS_DATAx register contents |

|------------|------------|------------|------------|---------------------------------------------------|-----------------------------|

| 0          | 1          | 0          | 0          | DSP write to SNS_DATAx_<br>X registers inhibited. | 0000h                       |

| 0          | 1          | 0          | 1          | DSP write to SNS_DATAx_<br>X registers inhibited. | AAAAh                       |

| 0          | 1          | 1          | 0          | DSP write to SNS_DATAx_<br>X registers inhibited. | 5555h                       |

| 0          | 1          | 1          | 1          | DSP write to SNS_DATAx_<br>X registers inhibited. | FFFFh                       |

### 7.3.2 ΣΔ converter

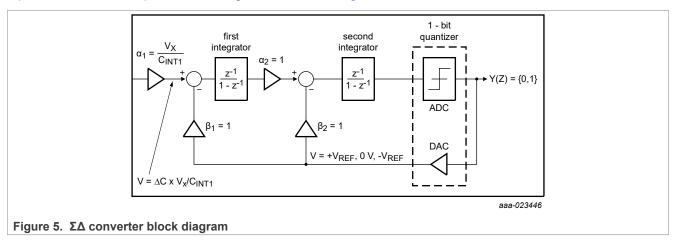

A second order sigma delta modulator converts the voltage from the analog front end to a data stream that is input to the DSP. A simplified block diagram is shown in <u>Figure 5</u>.

The sigma delta modulator operates at a frequency of 1 MHz, with the transfer function in Equation 1.

$$H(Z) = \frac{\alpha_1}{Z^2} \tag{1}$$

## 7.3.3 Digital signal processor (DSP)

A DSP is used to perform signal filtering and compensation. A diagram illustrating the signal processing flow within the DSP is shown in <u>Figure 6</u>.

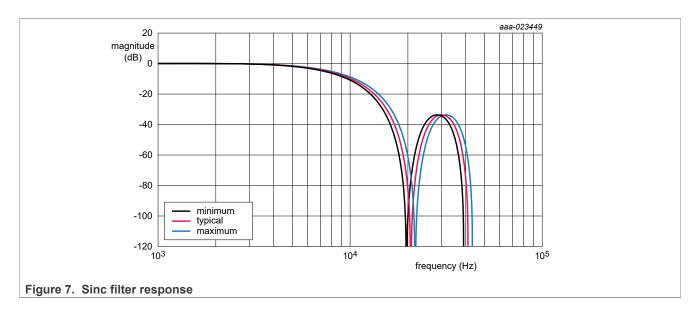

#### 7.3.3.1 Decimation sinc filter

In Equation 2, the output of the  $\Sigma\Delta$  modulator is decimated and converted to a parallel value by two third-order sinc filters; the first with a decimation ratio of 24 and the second with a decimation ratio of 4.

$$H(Z) = \left(\frac{1}{24^3}\right) \times \left(\frac{1 - Z^{-24}}{1 - Z^{-1}}\right)^3 \quad H(Z) = \left(\frac{1}{4^3}\right) \times \left(\frac{1 - Z^{-4}}{1 - Z^{-1}}\right)^3 \tag{2}$$

## 7.3.3.2 Signal trim and compensation

The device includes digital trim to compensate for sensor offset, sensitivity, and nonlinearity over temperature.

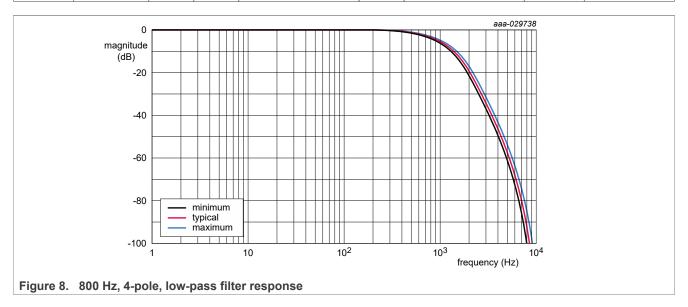

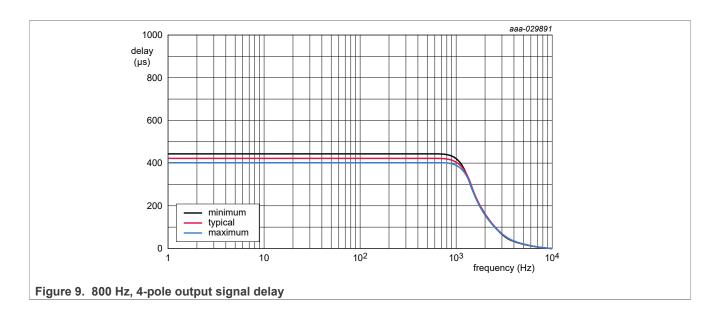

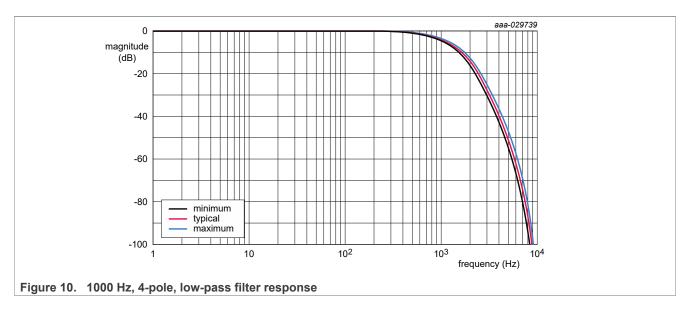

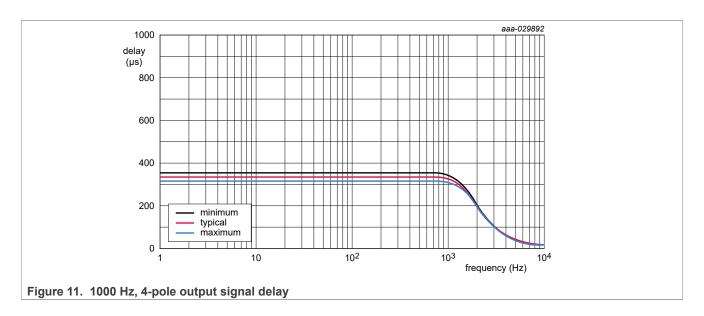

#### 7.3.3.3 Low-pass filter

Data from the sinc filter is processed by an infinite impulse response (IIR) low-pass filter with the transfer function and coefficients shown in <u>Equation 3</u>.

$$H(Z) = a_0 \times \frac{(n_{11} \times z^0) + (n_{12} \times z^{-1}) + (n_{13} \times z^{-2})}{(d_{11} \times z^0) + (d_{12} \times z^{-1}) + (d_{13} \times z^{-2})} \times \frac{(n_{21} \times z^0) + (n_{22} \times z^{-1}) + (n_{23} \times z^{-2})}{(d_{21} \times z^0) + (d_{22} \times z^{-1}) + (d_{23} \times z^{-2})}$$

(3)

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

Table 6. IIR low pass filter coefficients

| Filter<br>number | Typical –3 dB<br>frequency | Filter<br>order |                 | Filter coeffic    | cients (24 b    | oit)               | Group<br>delay (µs) | Typical<br>attenuation @<br>1000 Hz (dB) |

|------------------|----------------------------|-----------------|-----------------|-------------------|-----------------|--------------------|---------------------|------------------------------------------|

| 1                | 800 Hz                     | 4               | a <sub>0</sub>  | 0.088642612609670 | _               | _                  | 418                 | 4.95                                     |

|                  |                            |                 | n <sub>11</sub> | 0.029638050039039 | d <sub>11</sub> | 1                  |                     |                                          |

|                  |                            |                 | n <sub>12</sub> | 0.087543281056143 | d <sub>12</sub> | -1.422792640957290 |                     |                                          |

|                  |                            |                 | n <sub>13</sub> | 0.029695285913601 | d <sub>13</sub> | 0.511435253566960  |                     |                                          |

|                  |                            |                 | n <sub>21</sub> | 0.250241278804809 | d <sub>21</sub> | 1                  |                     |                                          |

|                  |                            |                 | n <sub>22</sub> | 0.499999767379068 | d <sub>22</sub> | -1.503329908017845 |                     |                                          |

|                  |                            |                 | n <sub>23</sub> | 0.249758953816089 | d <sub>23</sub> | 0.621996524706640  |                     |                                          |

| 2                | 1000 Hz                    | 4               | a <sub>0</sub>  | 0.129604264748411 | _               | _                  | 333                 | 2.99                                     |

|                  |                            |                 | n <sub>11</sub> | 0.043719804402508 | d <sub>11</sub> | 1                  |                     |                                          |

|                  |                            |                 | n <sub>12</sub> | 0.087543281056143 | d <sub>12</sub> | -1.300502656562698 |                     |                                          |

|                  |                            |                 | n <sub>13</sub> | 0.043823599710731 | d <sub>13</sub> | 0.430106921311110  |                     |                                          |

|                  |                            |                 | n <sub>21</sub> | 0.250296586927511 | d <sub>21</sub> | 1                  |                     |                                          |

|                  |                            |                 | n <sub>22</sub> | 0.499999648540934 | d <sub>22</sub> | -1.379959571988366 |                     |                                          |

|                  |                            |                 | n <sub>23</sub> | 0.249703764531484 | d <sub>23</sub> | 0.555046257157745  |                     |                                          |

## 7.3.3.4 Absolute pressure output data scaling equation

<u>Equation 4</u> is used to convert absolute pressure readings with the variables as specified in <u>Table 7</u>. Note, the specified values apply only if the P\_CAL\_ZERO value is set to 0000h.

$$PABS_{kPa} = \frac{PABS_{LSB} - PABSOFF_{LSB}}{PABS_{SENSE}}$$

(4)

Where:

$PABS_{kPa}$  = The absolute pressure output in kPa.

$PABS_{LSB}$  = The absolute pressure output in LSB.

PABSOFF<sub>LSB</sub> = The internal trimmed absolute pressure output value at 0 kPa in LSB.

PABS<sub>SENSE</sub> = The trimmed absolute pressure sensitivity in LSB/kPa.

Table 7. Scaling parameters

| Range              | Data reading                              | PABSOff <sub>LSB</sub> (LSB) | PABS <sub>SENSE</sub> (LSB/kPa) |

|--------------------|-------------------------------------------|------------------------------|---------------------------------|

|                    | 12-bit sensor data request <sup>[1]</sup> | 159                          | 7                               |

| 20 kPa - 550 kPa   | 16-bit register/data read 62h and 63h     | 28990                        | 14                              |

| 20 KF a - 330 KF a | Interrupt threshold registers 46h to 49h  | 28990                        | 14                              |

|                    | 16-bit sensor data request <sup>[2]</sup> | 2544                         | 112                             |

- [1] See <u>Section 7.7.8.1</u> for more details.

- [2] Applied scaling for Section 7.7.20.

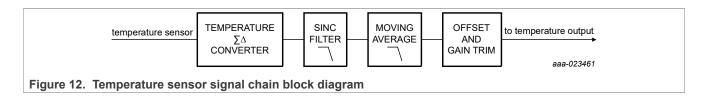

#### 7.3.4 Temperature sensor

## 7.3.4.1 Temperature sensor signal chain

The device includes a temperature sensor for signal compensation and user readability. <u>Figure 12</u> shows a simplified block diagram. Temperature sensor parameters are specified in <u>Table 104</u> and <u>Table 105</u>.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

## 7.3.4.2 Temperature sensor output scaling equation

Equation 5 is used to convert temperature readings with the variables specified in Table 8.

$$T_{DEGC} = \frac{T_{LSB} - T0_{LSB}}{T_{SENSE}} \tag{5}$$

Where:

T<sub>DEGC</sub> = The temperature output in degrees C

$T_{LSB}$  = The temperature output in LSB

T0<sub>LSB</sub> = The expected temperature output in LSB at 0 °C

T<sub>SENSE</sub> = The expected temperature sensitivity in LSB/°C

Table 8. Temperature conversion variables

| Data reading         | T0 <sub>LSB</sub> (LSB) | T <sub>SENSE</sub> LSB/C) |

|----------------------|-------------------------|---------------------------|

| 8-bit register read  | 68                      | 1                         |

| 16-bit register read | 17408                   | 256                       |

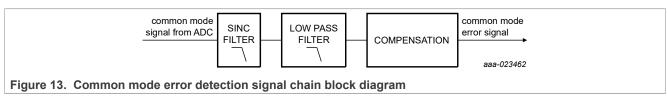

#### 7.3.5 Common mode error detection signal chain

The device includes a continuous pressure transducer common mode error detection. A simplified block diagram is shown in <u>Figure 13</u>. The common mode error signal is compared against the normal absolute pressure signal. If the comparison falls outside pre-determined limits, the CM\_ERROR bit in the DSP\_STAT register is set. Once the error condition is removed, the CM\_ERROR bit is cleared as specified in <u>Section 7.7.15</u> "DSP\_STAT - DSP specific status register (address 60h)".

# 7.4 Inter-integrated circuit (I<sup>2</sup>C) interface

The device includes an interface compliant to the NXP I<sup>2</sup>C-bus specification<sup>[4]</sup>. The device operates in client mode and includes support for standard mode, fast mode, and fast mode plus, although the maximum practical operating frequency for I<sup>2</sup>C in a given system implementation depends on several factors including the pull-up resistor values and the total bus capacitance.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

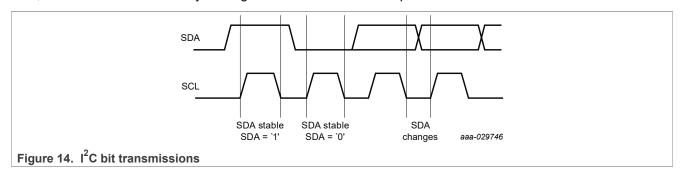

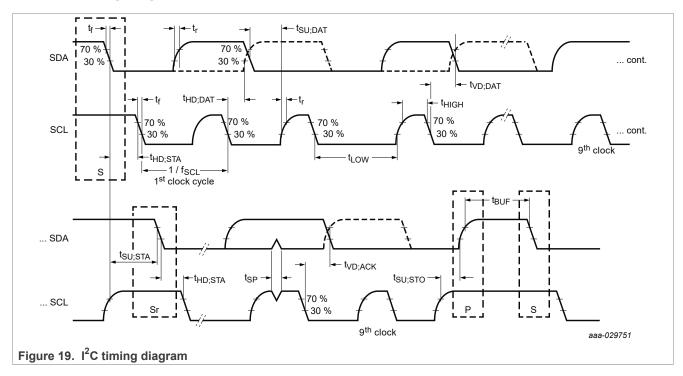

## 7.4.1 I<sup>2</sup>C bit transmissions

The state of SDA when SCL is high determines the bit value being transmitted. SDA must be stable when SCL is high and change when SCL is low as shown in <u>Figure 14</u>. After the START signal has been transmitted by the host, the bus is considered busy. Timing for the start condition is specified in <u>Table 105</u>.

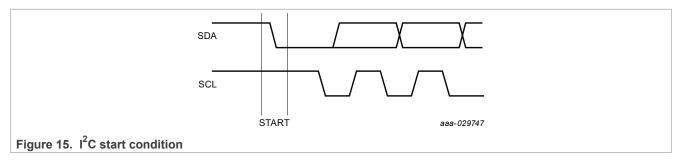

## 7.4.2 I<sup>2</sup>C start condition

A bus operation is always started with a start condition (START) from the host. A START is defined as a high to low transition on SDA while SCL is high as shown in <u>Figure 15</u>. After the START signal has been transmitted by the host, the bus is considered busy. Timing for the start condition is specified in <u>Table 105</u>.

A start condition (START) and a repeat START condition (rSTART) are identical.

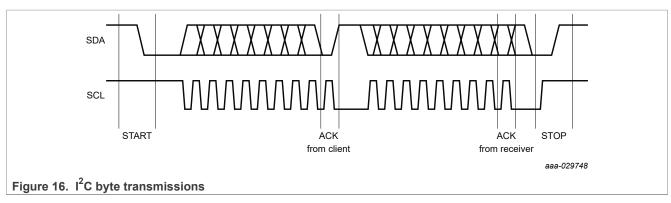

## 7.4.3 I<sup>2</sup>C byte transmission

Data transfers are completed in byte increments. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an acknowledge bit (Section 7.4.4 "I2C acknowledge and not acknowledge transmissions") from the receiver. Data is transferred with the most significant bit (MSB) first (see Figure 16). The host generates all clock pulses, including the ninth clock for the acknowledge bit. Timing for the byte transmissions is specified in Section 7.4.4 "I2C acknowledge and not acknowledge transmissions". All functions for this device are completed within the acknowledge clock pulse. Clock stretching is not used.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

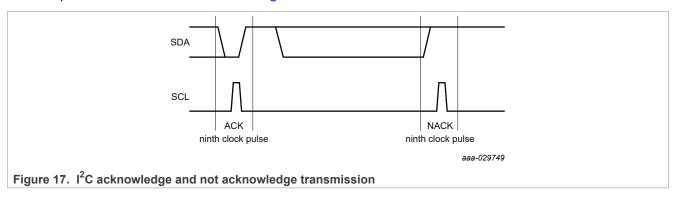

## 7.4.4 I<sup>2</sup>C acknowledge and not acknowledge transmissions

Each byte must be followed by an acknowledge bit (ACK) from the receiver. For an ACK, the transmitter releases SDA during the acknowledge clock pulse and the receiver pulls SDA low during the high portion of the clock pulse. Set up and hold times as specified in <u>Table 105</u> must also be taken into account.

For a not acknowledge bit (NACK), SDA remains high during the entire acknowledge clock pulse. Five conditions lead to a NACK:

- 1. No receiver is present on the bus with the transmitted address.

- 2. The addressed receiver is unable to receive or transmit because it is performing some real-time function and is not ready to start communication with the host.

- 3. The receiver receives unrecognized data or commands.

- 4. The receiver cannot receive any more data bytes.

- 5. The host-receiver signals the end of the transfer to the client transmitter.

Following a NACK, the host can transmit either a STOP to terminate the transfer, or a repeated START to initiate a new transfer.

An example ACK and NACK are shown in Figure 17.

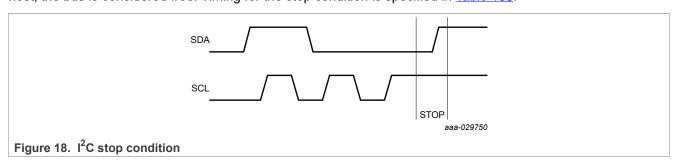

# 7.4.5 I<sup>2</sup>C stop condition

A bus operation is always terminated with a stop condition (STOP) from the host. A STOP is defined as a low to high transition on SDA while SCL is high as shown in <u>Figure 18</u>. After the STOP has been transmitted by the host, the bus is considered free. Timing for the stop condition is specified in <u>Table 105</u>.

# 7.4.6 I<sup>2</sup>C register transfers

## 7.4.6.1 Register write transfers

The device supports I<sup>2</sup>C register write data transfers. Register write data transfers are constructed as follows:

1. The host transmits a START condition.

FXPS7550D48

All information provided in this document is subject to legal disclaimers.

- 2. The host transmits the 7-bit client address.

- 3. The host transmits a '0' for the read/write bit to indicate a write operation.

- 4. The client transmits an ACK.

- 5. The host transmits the register address to be written.

- 6. The client transmits an ACK.

- 7. The host transmits the data byte to be written to the register address.

- 8. The client transmits an ACK.

- 9. The host transmits a STOP condition.

The device automatically increments the register address allowing for multiple register writes to be completed in one transaction. In this case, the register write data transfers are constructed as follows:

- 1. The host transmits a START condition.

- 2. The host transmits the 7-bit client address.

- 3. The host transmits a '0' for the read/write bit to indicate a write operation.

- 4. The client transmits an ACK.

- 5. The host transmits the register address to be written.

- 6. The client transmits an ACK.

- 7. The host transmits the data byte to be written to the register address.

- 8. The client transmits an ACK.

- 9. The host transmits the data byte to be written to the register address +1.

- 10. The client transmits an ACK.

- 11. Repeat steps 9 and 10 until all registers are written.

- 12. The host transmits a STOP condition.

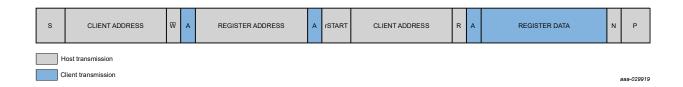

## 7.4.6.2 Register read transfers

The device supports I<sup>2</sup>C register read data transfers. Register read data transfers are constructed as follows:

- 1. The host transmits a START condition.

- 2. The host transmits the 7-bit client address.

- 3. The host transmits a '0' for the read/write bit to indicate a write operation.

- 4. The client transmits an ACK.

- 5. The host transmits the register address to be read.

- 6. The client transmits an ACK.

- 7. The host transmits a repeat START condition.

- 8. The host transmits the 7-bit client address.

- 9. The host transmits a '1' for the read/write bit to indicate a read operation.

- 10. The client transmits an ACK.

- 11. The client transmits the data from the register addressed.

- 12. The host transmits a NACK.

- 13. The host transmits a STOP condition.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

## 7.4.6.3 Sensor data register read wrap around

The device includes automatic sensor data register read wrap-around features to optimize the number of I<sup>2</sup>C transactions necessary for continuous reads of sensor data. Depending on the state of the SIDx\_EN bits in the SOURCEID\_0 and SOURCEID\_1 registers, the register address automatically wraps back to the DEVSTAT\_COPY register as shown in Table 9.

Table 9. Sensor data register read wrap-around description

| SID1_EN | SID0_EN | Address increment and wrap-around effect                      | Optimized register-read sequence                                                                                                       |

|---------|---------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0       | Address wraps around from FFh to 00h                          | None                                                                                                                                   |

| 0       | 1       | Address wraps from 63h (SNSDATA0_H) to 61h (DEVSTAT_COPY)     | DEVSTAT_COPY, SNSDATA0_L, SNSDATA0_H                                                                                                   |

| 1       | 0       | Address wraps from 65h (SNSDATA1_H) to 61h (DEVSTAT_COPY)     | DEVSTAT_COPY, SNSDATA0_L, SNSDATA0_H,<br>SNSDATA1_L, SNSDATA1_H                                                                        |

| 1       | 1       | Address wraps from 69h (SNSDATA0_TIME3) to 61h (DEVSTAT_COPY) | DEVSTAT_COPY, SNSDATA0_L, SNSDATA0_H,<br>SNSDATA1_L, SNSDATA1_H, SNSDATA0_TIME0,<br>SNSDATA0_TIME1, SNSDATA0_TIME2, SNSDATA0_<br>TIME3 |

# 7.4.7 I<sup>2</sup>C timing diagram

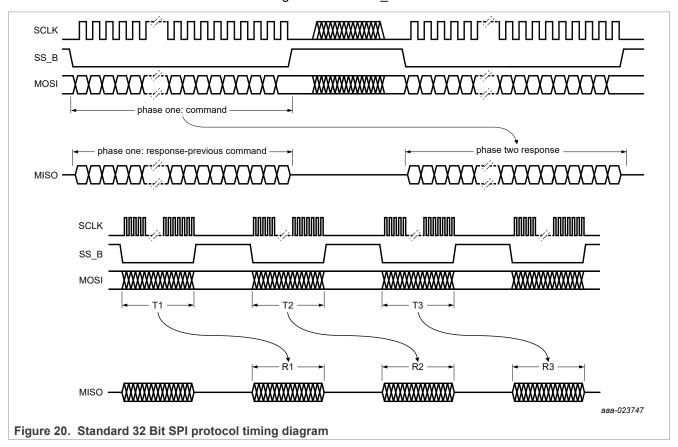

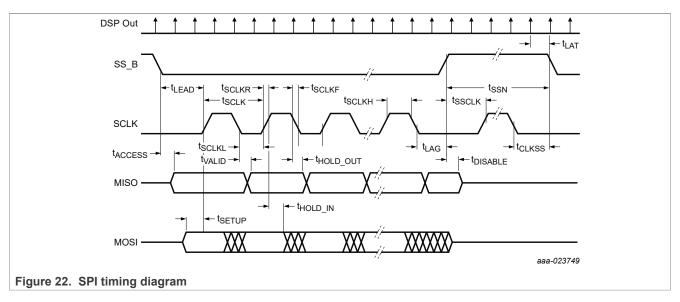

## 7.5 Standard 32-bit SPI protocol

The device includes a standard SPI protocol requiring 32-bit data packets. The device is a client device and requires a low base clock value (CPOL = 0) with data captured on the rising edge of the clock and data propagated on the falling edge of the clock (CPHA = 0). The most significant bit is transferred first (MSB first). SPI transfers are completed through a sequence of two phases. During the first phase, the command is transmitted from the SPI host to the device. During the second phase, response data is transmitted from the client device. MOSI and SCLK transitions are ignored when SS B is not asserted.

#### 7.5.1 SPI command format

There are two SPI commands as shown in <u>Table 10</u>. These are the Register Access command and the Sensor Data command.

The Register Access command is a standard SPI read and write command which access the registers and are defined by field descriptions shown in <u>Section 7.5.3.1</u> through <u>Section 7.5.3.2</u>.

The Sensor Data command provides additional information such as basic and detailed sensor status if needed as defined by field descriptions shown in Section 7.5.3.3.

#### Table 10. SPI command format

MSB: bit 31; LSB: bit 0

| 31 | 30                                                           | 29   | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20    | 19    | 18    | 17    | 16         | 15      | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7        | 6 | 5 | 4     | 3     | 2 | 1 0 |

|----|--------------------------------------------------------------|------|----|----|----|----|----|----|----|----|-------|-------|-------|-------|------------|---------|------|----|----|----|----|---|---|----------|---|---|-------|-------|---|-----|

|    |                                                              |      |    |    |    |    |    |    |    |    |       |       | Re    | egist | er access  | s con   | nmaı | ıd |    |    |    |   |   |          |   |   |       |       |   |     |

|    | Command Fixed bits: Register address Register data must = 0h |      |    |    |    |    |    |    |    |    |       |       |       |       | 8-bit CRC  |         |      |    |    |    |    |   |   |          |   |   |       |       |   |     |

|    | C[3                                                          | 3:0] |    | 0  | 0  | 0  | 0  |    |    | R  | A[7:1 | ]     |       |       | RA[0]      | RD[7:0] |      |    |    |    |    |   |   | CRC[7:0] |   |   |       |       |   |     |

|    |                                                              |      |    |    |    |    |    |    |    |    |       |       |       | Sens  | or data o  | omn     | nand |    |    |    |    |   |   |          |   |   |       |       |   |     |

|    | Com                                                          | mand | i  |    |    |    |    |    |    |    | Fi    | xed l | bits: | mus   | t = 0 0000 | )h      |      |    |    |    |    |   |   |          |   | 1 | 8-bit | CRC   | ; |     |

|    | C[3                                                          | 3:0] |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0     | 0     | 0     | 0          | 0       | 0    | 0  | 0  | 0  | 0  | 0 | 0 |          |   |   | CRC   | [7:0] |   |     |

## Table 11. SPI command summary

|   | C[    | 3:0] |   | Command type                                 | Data source SOURCEID[2:0] = C[3:1] <sup>[1]</sup> |  |  |  |  |  |  |

|---|-------|------|---|----------------------------------------------|---------------------------------------------------|--|--|--|--|--|--|

| 0 | 0     | 0    | 0 | Unused Command (reserved for error response) | NA                                                |  |  |  |  |  |  |

| 0 | 0     | 0    | 1 | Sensor Data Request                          | SOURCEID = 0h                                     |  |  |  |  |  |  |

| 0 | 0     | 1    | 0 | reserved Command                             | NA                                                |  |  |  |  |  |  |

| 0 | 0     | 1    | 1 | Sensor Data Request                          | SOURCEID = 1h                                     |  |  |  |  |  |  |

| 0 | 1     | 0    | 0 | reserved Command                             | NA                                                |  |  |  |  |  |  |

| 0 | 1     | 0    | 1 | Sensor Data Request                          | SOURCEID = 2h                                     |  |  |  |  |  |  |

| 0 | 1     | 1    | 0 | reserved Command                             | NA                                                |  |  |  |  |  |  |

| 0 | 1     | 1    | 1 | Sensor Data Request                          | SOURCEID = 3h                                     |  |  |  |  |  |  |

| 1 | 0     | 0    | 0 | Register Write Request <sup>[2]</sup>        | NA                                                |  |  |  |  |  |  |

| 1 | 0     | 0    | 1 | Sensor Data Request                          | SOURCEID = 4h                                     |  |  |  |  |  |  |

| 1 | 0     | 1    | 0 | reserved Command                             | NA                                                |  |  |  |  |  |  |

| 1 | 0     | 1    | 1 | Sensor Data Request                          | SOURCEID = 5h                                     |  |  |  |  |  |  |

| 1 | 1     | 0    | 0 | Register Read Request <sup>[3]</sup>         | NA                                                |  |  |  |  |  |  |

| 1 | 1     | 0    | 1 | Sensor Data Request                          | SOURCEID = 6h                                     |  |  |  |  |  |  |

| 1 | 1     | 1    | 0 | Reserved Command                             | NA                                                |  |  |  |  |  |  |

| 1 | 1 1 1 |      | 1 | Sensor Data Request                          | SOURCEID = 7h                                     |  |  |  |  |  |  |

Source identification code matching the value set in the SOURCEID\_X field in register 1Ah and 1Bh for the requested sensor data. Also see Section 7.5.3.3.2 "Sensor data request response message format", Table 22 and Table 24.

See Section 7.5.3.2.1.

See Section 7.5.3.1.1. [1]

## 7.5.2 SPI response format

#### Table 12. SPI response format

MSB: bit 31; LSB: bit 0

| 31 | 30    | 29    | 28 | 27                                                    | 26         | 25             | 24                    | 23  | 22   | 21  | 20   | 19    | 18    | 17    | 16   | 15              | 14    | 13              | 12     | 11              | 10   | 9                      | 8    | 7         | 6 | 5 |    | 4 3    | 2  |  | 1 0 |

|----|-------|-------|----|-------------------------------------------------------|------------|----------------|-----------------------|-----|------|-----|------|-------|-------|-------|------|-----------------|-------|-----------------|--------|-----------------|------|------------------------|------|-----------|---|---|----|--------|----|--|-----|

|    |       |       |    |                                                       |            |                |                       |     |      |     | ı    | Resp  | ons   | e to  | Regi | ster            | Rec   | uest            |        |                 |      |                        |      |           |   |   |    |        |    |  |     |

|    | Comi  | mand  |    | Ba<br>Sta                                             |            | Unu<br>Da<br>0 | ta                    |     |      |     |      | ta: c |       |       |      |                 | R     | egiste<br>of RA |        |                 |      |                        |      | 8-bit CRC |   |   |    |        |    |  |     |

|    | C[0], | [3:1] |    | ST[                                                   | 1:0]       | 0              | 0                     |     |      |     | RD[1 | 15:8] |       |       |      |                 |       |                 | RD     | [7:0]           |      |                        |      |           |   |   | С  | RC[7:0 | )] |  |     |

|    |       |       |    |                                                       |            |                |                       |     |      |     | Re   | spo   | nse   | to Se | enso | r Dat           | a R   | eques           | t      |                 |      |                        |      |           |   |   |    |        |    |  |     |

|    | Comi  | mand  |    | Basic Sensor Data Detail Status Status                |            |                |                       |     |      |     |      |       |       |       |      |                 |       | 8-              | bit CR | С               |      |                        |      |           |   |   |    |        |    |  |     |

|    | C[0], | [3:1] |    | ST[1:0]   SD[11:0]   Optional SD resolution   SF[1:0] |            |                |                       |     |      |     |      |       |       |       |      |                 | 1:0]  |                 |        |                 | С    | RC[7:0                 | )]   |           |   |   |    |        |    |  |     |

|    |       |       |    |                                                       |            |                |                       |     |      |     | Err  | or R  | espo  | onse  | to R | egist           | ter F | Reque           | st     |                 |      |                        |      |           |   |   |    |        |    |  |     |

|    | Comi  | mand  |    | Ba<br>Sta                                             |            |                |                       |     |      |     | U    | nuse  | ed Da | ata = | 000  | 0h              |       |                 |        |                 |      | De <sup>s</sup><br>Sta |      |           |   |   | 8- | bit CR | С  |  |     |

|    | C[0], | [3:1] |    | 1                                                     | 1          | 0              | 0 0 0 0 0 0 0 0 0 0 0 |     |      |     |      |       |       |       | 0    | 0 0 0 0 SF[1:0] |       |                 |        |                 |      | CRC[7:0]               |      |           |   |   |    |        |    |  |     |

|    |       |       |    |                                                       |            |                |                       | E   | rror | Res | oons | se to | Sen   | sor   | Data | Req             | ues   | t With          | Sen    | sor [           | Data |                        |      |           |   |   |    |        |    |  |     |

|    | Comi  | mand  |    | Ba<br>Sta                                             | sic<br>tus |                |                       |     |      |     |      | S     | ensc  | or Da | ta   |                 |       |                 |        |                 |      | De <sup>*</sup><br>Sta |      |           |   |   | 8- | bit CR | С  |  |     |

|    | C[0], | [3:1] |    | 1                                                     | 1          |                |                       |     |      |     | SD[1 | 11:0] |       |       |      |                 |       |                 |        | nal S<br>lution |      | SF[                    | 1:0] |           |   |   | С  | RC[7:0 | )] |  |     |

|    |       |       |    |                                                       |            |                |                       | Err | or R | esp | nse  | to S  | ens   | or Da | ta R | eque            | est \ | Vitho           | ut Se  | nsor            | Dat  | ta                     |      |           |   |   |    |        |    |  |     |

|    | Comi  | mand  |    | Ba<br>Sta                                             |            | х              |                       |     |      |     |      | Unu   | ised  | Data  | = 00 | 000h            |       |                 |        |                 |      | De <sup>s</sup><br>Sta |      |           |   |   | 8- | bit CR | С  |  |     |

| 0  | 0     | 0     | 0  | 1                                                     | 1          | х              | 0                     | 0   | 0    | 0   | 0    | 0     | 0     | 0     | 0    | 0               | 0     | 0               | 0      | 0               | 0    | SF[                    | 1:0] |           |   |   | С  | RC[7:0 | )] |  |     |

## 7.5.3 Command summary

#### 7.5.3.1 Register read command

The device supports a register read command. The register read command uses the upper 7 bits of the addresses defined in <u>Section 7.6 "User-accessible data array"</u> to address 8-bit registers in the register map.

The response to a register read command is shown in <u>Section 7.5.3.1.2 "Register read response message format"</u>. The response is transmitted on the next SPI message if and only if all of the following conditions are met:

- No SPI error is detected (see Section 7.5.5.3 "SPI error")

- No MISO error is detected (see Section 7.5.5.4 "SPI data output verification error")

If these conditions are met, the device responds to the register read request as shown in <a href="Section 7.5.3.1.2" "Register read response message format"</a>. Otherwise, the device responds with the error response as defined in <a href="Section 7.5.5.2" "Detailed status field"</a>. The register read response includes the register contents at the rising edge of SS\_B for the register read command.

## 7.5.3.1.1 Register read command message format

Table 13. Register read command message format

MSB: bit 31; LSB: bit 0

| 31 | 30          | 29           | 28 | 27 | 26           | 25 | 24 | 23 | 22 | 21 | 20     | 19    | 18    | 17    | 16        | 15  | 14  | 13 | 12    | 11    | 10  | 9 | 8 | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

|----|-------------|--------------|----|----|--------------|----|----|----|----|----|--------|-------|-------|-------|-----------|-----|-----|----|-------|-------|-----|---|---|---|---|---|-------|-------|---|---|---|

|    |             |              |    |    |              |    |    |    |    |    |        |       | R     | egist | er access | com | mar | d  |       |       |     |   |   |   |   |   |       |       |   |   |   |

|    | Comi<br>C[3 | mano<br>3:0] | t  | 1  | ixed<br>must |    |    |    |    | Re | egiste | er ac | ldres | s     |           |     |     | R  | egist | er da | ita |   |   |   |   |   | 8-bit | CRC   |   |   |   |

| 1  | 1           | 0            | 0  | 0  | 0            | 0  | 0  |    |    | R  | A[7:1  | ]     |       |       | RA[0]     | 0   | 0   | 0  | 0     | 0     | 0   | 0 | 0 |   |   |   | CRC   | [7:0] |   |   |   |

Table 14. Register read command message bit field descriptions

| Bit field | Definition                                                    |

|-----------|---------------------------------------------------------------|

| C[3:0]    | Register read command = '1100'                                |

| RA[7:0]   | RA[7:1] contains the word address of the register to be read. |

| CRC[7:0]  | Read CRC Section                                              |

### 7.5.3.1.2 Register read response message format

#### Table 15. Register read response message format

MSB: bit 31; LSB: bit 0

| 31 | 30 | 29            | 28 | 27         | 26   | 25 | 24          | 23 | 22 | 21            | 20   | 19   | 18    | 17     | 16   | 15  | 14  | 13             | 12  | 11   | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

|----|----|---------------|----|------------|------|----|-------------|----|----|---------------|------|------|-------|--------|------|-----|-----|----------------|-----|------|----|---|---|---|---|---|-------|-------|---|---|---|

|    |    |               |    |            |      |    |             |    |    |               |      | R    | egist | ter ac | cess | com | man | d              |     |      |    |   |   |   |   |   |       |       |   |   |   |

|    |    | mano<br>[3:1] |    | Ba:<br>Sta |      |    | sed<br>a 0h |    |    | giste<br>f RA |      |      |       |        |      |     |     | giste<br>of RA |     |      |    |   |   |   |   | 8 | 3-bit | CRC   | ; |   |   |

| 0  | 1  | 1             | 0  | ST[        | 1:0] | 0  | 0           |    |    |               | RD[1 | 5:8] |       |        |      |     |     |                | RD[ | 7:0] |    |   |   |   |   |   | CRC   | [7:0] |   |   |   |

Table 16. Register read response message bit field descriptions

| Bit field   | Definition                                                              |

|-------------|-------------------------------------------------------------------------|

| C[0], [3:1] | Register Read Command = '0110'                                          |

| ST[1:0]     | Status                                                                  |

| RD[15:8]    | The contents of the register addressed by RA[7:1] high byte (RA[0] = 1) |

| RD[7:0]     | The contents of the register addressed by RA[7:1] low byte (RA[0] = 0)  |

| CRC[7:0]    | 8-bit CRC                                                               |

## 7.5.3.2 Register write command

The device supports a register write command. The register write command writes the value specified in RD[7:0] to the register addressed by RA[7:0].

The response to a register write command is shown in <u>Section 7.5.3.2.2 "Register write response message format"</u>. The register write is executed and a response is transmitted on the next SPI message if and only if all of the following conditions are met:

- No SPI error is detected (see Section 7.5.5.3 "SPI error")

- No MISO error is detected (see Section 7.5.5.4 "SPI data output verification error")

- · The ENDINIT bit is cleared.

- This applies to all registers except for the RESET[1:0] bits in the DEVLOCK WR register

- · No invalid register request is detected as described below.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

If these conditions are met, the register write is executed and the device responds to the register write request as shown in <u>Section 7.5.3.2.2 "Register write response message format"</u>. Otherwise, no register is written and the device responds with the error response as defined in <u>Section 7.5.2 "SPI response format"</u>. The register is not written until the transfer during which the register write was requested has been completed.

A register write command to a read-only register is not executable, but results in a valid response.

## 7.5.3.2.1 Register write command message format

Table 17. Register write command message format

MSB: bit 31: LSB: bit 0

| 31 | 30         | 29           | 28 | 27 | 26           | 25 | 24 | 23 | 22 | 21 | 20    | 19    | 18   | 17    | 16        | 15  | 14  | 13 | 12    | 11    | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

|----|------------|--------------|----|----|--------------|----|----|----|----|----|-------|-------|------|-------|-----------|-----|-----|----|-------|-------|----|---|---|---|---|---|-------|-------|---|---|---|

|    |            |              |    |    |              |    |    |    |    |    |       |       | R    | egist | er access | com | man | d  |       |       |    |   |   |   |   |   |       |       |   |   |   |

|    | Com<br>C[3 | manc<br>3:0] | t  |    | ixed<br>nust |    |    |    |    | R  | egist | er ac | dres | s     |           |     |     | Re | giste | er da | ta |   |   |   |   | 8 | 3-bit | CRC   | ; |   |   |

| 1  | 0          | 0            | 0  | 0  | 0            | 0  | 0  |    |    | R  | A[7:1 | 1]    |      |       | RA[0]     |     |     |    | RD[   | 7:0]  |    |   |   |   |   |   | CRC   | [7:0] |   |   |   |

Table 18. Register write command message bit field descriptions

| Bit field | Definition                                                      |

|-----------|-----------------------------------------------------------------|

| C[3:0]    | Register write command = '1000'                                 |

| RA[7:0]   | RA[7:1] contains the byte address of the register to be written |

| RD[7:0]   | RD[7:0] contains the data byte to be written to address RA[7:0] |

| CRC[7:0]  | 8-bit CRC                                                       |

### 7.5.3.2.2 Register write response message format

Table 19. Register write response message format

MSB: bit 31; LSB: bit 0

| 31 30 29 28                | 27 26           | 25 24                | 23 22 21 20 19 18 17 16                         | 15 14 13 12 11 10 9 8                          | 7 6 5 4 3 2 1 0 |

|----------------------------|-----------------|----------------------|-------------------------------------------------|------------------------------------------------|-----------------|

|                            |                 |                      | Register acces                                  | s command                                      |                 |

| <b>Command</b> C[0], [3:1] | Basic<br>Status | Unused<br>Data<br>0h | Register data: contents<br>of RA[7:1] high byte | Register data: contents<br>of RA[7:1] low byte | 8-bit CRC       |

| 0 1 0 0                    | ST[1:0]         | 0 0                  | RD[15:8]                                        | RD[7:0]                                        | CRC[7:0]        |

Table 20. Register write response message bit field descriptions

| Bit field   | Definition                                                              |

|-------------|-------------------------------------------------------------------------|

| C[0], [3:1] | Register Read Command = '0100'                                          |

| ST[1:0]     | Status                                                                  |

| RD[15:8]    | The contents of the register addressed by RA[7:1] high byte (RA[0] = 1) |

| RD[7:0]     | The contents of the register addressed by RA[7:1] low byte (RA[0] = 0)  |

| CRC[7:0]    | 8-bit CRC                                                               |

#### 7.5.3.3 Sensor data request commands

The device supports standard sensor data request commands. The sensor data request command format is described in <u>Section 7.5.3.3.1 "Sensor data request command message format"</u>. The response to a sensor data request is shown in <u>Section 7.5.3.3.2 "Sensor data request response message format"</u>. The response is transmitted on the next SPI message subject to the error handling conditions specified in <u>Section 7.5.5</u>

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

<u>"Exception handling"</u>. The sensor data included in the response is the sensor data at the falling edge of SS\_B for the sensor data request response.

## 7.5.3.3.1 Sensor data request command message format

#### Table 21. Sensor data request command message format

MSB: bit 31: LSB: bit 0

| 31 | 30  | 29   | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20   | 19    | 18    | 17    | 16   | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

|----|-----|------|----|----|----|----|----|----|----|----|------|-------|-------|-------|------|-----|----|----|----|----|----|---|---|---|---|---|-------|-------|---|---|---|

|    | Com | mand | ı  |    |    |    |    |    |    |    | Fixe | d bit | ts: m | ust = | 0 00 | 00h |    |    |    |    |    |   |   |   |   | ; | 8-bit | CRC   |   |   |   |

|    | C[3 | 3:0] |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0     | 0     | 0     | 0    | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   |   |   | CRC   | [7:0] |   |   |   |

#### Table 22. Sensor data request command message bit field descriptions

| Bit field              | Definition                                               |

|------------------------|----------------------------------------------------------|

| C[0]                   | Sensor data request command = '1'                        |

| C[3:1] = SOURCEID[2:0] | Source identification code for the requested sensor data |

| CRC[7:0]               | 8-bit CRC                                                |

#### 7.5.3.3.2 Sensor data request response message format

## Table 23. Sensor data request response message format – 12 bit data length

MSB: bit 31; LSB: bit 0

| 31 | 30   | 29      | 28 | 27         | 26   | 25 | 24 | 23 | 22 | 21 | 20   | 19    | 18   | 17   | 16 | 15 | 14 | 13 | 12 | 11              | 10 | 9          | 8    | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

|----|------|---------|----|------------|------|----|----|----|----|----|------|-------|------|------|----|----|----|----|----|-----------------|----|------------|------|---|---|---|-------|-------|---|---|---|

|    | Com  | mano    | i  | Ba:<br>Sta |      |    |    |    | •  |    |      | S     | enso | r Da | ta |    |    |    |    |                 |    | Det<br>Sta |      |   |   |   | 8-bit | CRC   | ; |   |   |

|    | C[0] | , [3:1] |    | ST[        | 1:0] |    |    |    |    |    | SD[1 | 11:0] |      |      |    |    |    |    |    | nal SI<br>ution |    | SF[        | 1:0] |   |   |   | CRC   | [7:0] |   |   |   |

Table 24. Sensor data request response message bit field descriptions

| Bit field              | Definition                                                 |

|------------------------|------------------------------------------------------------|

| C[0]                   | Sensor data request command = '1'                          |

| C[3:1] = SOURCEID[2:0] | Source identification code for the requested sensor data   |

| ST[1:0]                | Basic Status                                               |

| SD[11:0]               | Sensor data                                                |

| Optional SD resolution | Optional for 16-bit Sensor data. Refer to Section 7.3.3.4. |

| SF[1:0]                | Detailed status                                            |

| CRC[7:0]               | 8-bit CRC                                                  |

#### 7.5.3.4 Reserved commands

The device responds to reserved commands on the next SPI message subject to the error handling conditions specified in <u>Section 7.5.5 "Exception handling"</u>.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

## 7.5.3.4.1 Reserved command message format

Table 25. Reserved command message format

MSB: bit 31; LSB: bit 0

| 31 | 30   | 29   | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7         | 6 | 5 | 4   | 3     | 2 | 1 | 0 |

|----|------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|-----------|---|---|-----|-------|---|---|---|

| (  | Comr | nand | I  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х | 8-bit CRC |   |   |     |       |   |   |   |

| 0  | 0    | 0    | 0  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х |           |   |   | CRC | [7:0] |   |   |   |

| 0  | 0    | 1    | 0  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х | CRC[7:0]  |   |   |     |       |   |   |   |

| 0  | 1    | 0    | 0  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х |           |   |   | CRC | [7:0] |   |   |   |

| 0  | 1    | 1    | 0  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х |           |   |   | CRC | [7:0] |   |   |   |

| 1  | 0    | 1    | 0  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х | CRC[7:0]  |   |   |     |       |   |   |   |

| 1  | 1    | 1    | 0  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х  | х | х |           |   |   | CRC | [7:0] |   |   |   |

Table 26. Reserved command message bit field descriptions

| Bit field | Definition       |

|-----------|------------------|

| C[3:0]    | Reserved command |

| CRC[7:0]  | 8-bit CRC        |

### 7.5.3.4.2 Reserved command response message format

#### Table 27. Reserved command response message format

MSB: bit 15; LSB: bit 0

| 31 | 30                                    | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19        | 18  | 17    | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|---------------------------------------|----|----|----|----|----|----|----|----|----|----|-----------|-----|-------|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Co | Command Echo Data                     |    |    |    |    |    |    |    |    |    |    | 8-bit CRC |     |       |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| х  | x x x x x x x x x x x x x x x x x x x |    |    |    |    |    |    |    | х  |    |    |           | CRC | [7:0] |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Table 28. Reserved command response message bit field descriptions

| Bit field    | Definition                       |

|--------------|----------------------------------|

| Command echo | Reserved command echo. Undefined |

| Data         | Response data. Undefined         |

| CRC[7:0]     | 8-bit CRC                        |

## 7.5.4 Error checking

#### 7.5.4.1 Default 8-bit CRC

#### 7.5.4.1.1 Command error checking

The device calculates an 8-bit CRC on the entire 32 bits of each command. Message data is entered into the CRC calculator MSB first, consistent with the transmission order of the message. If the calculated CRC does not match the transmitted CRC, the command is ignored and the device responds with the SPI error response.

The CRC decoding procedure is as follows:

- 1. A seed value is preset into the LSB of the shift register.

- 2. Using a serial CRC calculation method, the receiver rotates the received message and CRC into the LSB of the shift register in the order received (MSB first).

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

- 3. When the calculation on the last bit of the CRC is rotated into the shift register, the shift register contains the CRC check result.

- 4. If the shift register contains all zeros, the CRC is correct.

- 5. If the shift register contains a value other than zero, the CRC is incorrect.

The CRC polynomial and seed are shown in Table 29.

Table 29. SPI Command Message CRC

| SPICRCSEED[3:0] | Default Polynomial              | Default non-direct Seed |

|-----------------|---------------------------------|-------------------------|

| 0000            | $x^8 + x^5 + x^3 + x^2 + x + 1$ | 1111 1111               |

| non-zero        | $x^8 + x^5 + x^3 + x^2 + x + 1$ | 1111 SPICRCSEED[3:0]    |

## 7.5.4.1.2 Response error checking

The device calculates a CRC on the entire 32 bits of each response. Message data is entered into the CRC calculator MSB first, consistent with the transmission order of the message.

The CRC encoding procedure is as follows:

- 1. A seed value is preset into the LSB of the shift register.

- 2. Using a serial CRC calculation method, the transmitter rotates the transmitted message and CRC into the LSB of the shift register (MSB first).

- 3. Following the transmitted message, the transmitter feeds 8 zeros into the shift register, to match the length of the CRC.

- 4. When the last zero is fed into the input adder, the shift register contains the CRC.

- 5. The CRC is transmitted.

The CRC polynomial and seed are shown in <u>Table 30</u>.

Table 30. SPI Response Message CRC

| SPICRCSEED[3:0] | Default Polynomial              | Default non-direct Seed |

|-----------------|---------------------------------|-------------------------|

| 0000            | $x^8 + x^5 + x^3 + x^2 + x + 1$ | 1111 1111               |

| nonzero         | $x^8 + x^5 + x^3 + x^2 + x + 1$ | 1111 SPICRCSEED[3:0]    |

### 7.5.5 Exception handling

After POR, there a supply error flag is set. Expected initial responses with first 4 commands are shown in Table 31.

Table 31. Expected initial responses after t<sub>POR DataValid</sub> post POR

| Table 01. Expected initial respondes after tpor_Datavalle per |                                        |

|---------------------------------------------------------------|----------------------------------------|

| Command                                                       | Response                               |

| Command 1 (DEVSTAT READ)                                      | Ignore response 1                      |

| Command 2 (DEVSTAT READ)                                      | Ignore response 2                      |

| Command 3 (DEVSTAT READ)                                      | Ignore response 3                      |

| Command 4 (ANY USER COMMAND)                                  | Response 4 - 0X6080XXXX <sup>[1]</sup> |

<sup>[1]</sup> Response 4 is 0x6080XXXX after t<sub>POR\_DataValid</sub> wait time from POR. Otherwise only after t<sub>POR\_I2C/POR\_SPI</sub> wait time from POR, response would be 0x6081 XXXX due to DEVINIT bit still set to 1.

Before soft reset, write SOURCEID\_0 in address 1Ah with a non-zero value. Address 1Ah is read back to check soft reset sanity.

FXPS7550D4S

All information provided in this document is subject to legal disclaimers.

During soft reset, flash contents are reloaded into the mirror registers and during this process the supply error flag can get set based on device variation, temperature, and so forth. After 1 ms delay, the expected initial response from the first 5 commands are shown in Table 32.

Table 32. Expected initial responses after tpoR DataValid post soft reset

| Command                      | Response                                                   |

|------------------------------|------------------------------------------------------------|

| Command 1 (DEVSTAT READ)     | Ignore response 1                                          |

| Command 2 (DEVSTAT READ)     | Ignore response 2                                          |

| Command 3 (DEVSTAT READ)     | Ignore response 3                                          |

| Command 4 (SOURCEID_0 READ)  | Response 4 - 0X6080XXXX <sup>[1]</sup>                     |

| Command 5 (ANY USER COMMAND) | Response 5 - valid response with reset value of SOURCEID_0 |

<sup>[1]</sup> Response 4 is 0x6080XXXX after t<sub>POR\_DataValid</sub> wait time from soft reset. Otherwise only after t<sub>POR\_I2C/POR\_SPI</sub> wait time from soft reset, response 4 would be 0x6081XXXX due to DEVINIT bit still set to 1.

#### 7.5.5.1 Basic status field

All responses include a status field (ST[1:0]) that includes the general status of the device and transmitted data as described below. The contents of the status field is a representation of the device status at the rising edge of SS B for the previous SPI command.

Table 33. Basic status field for responses to register commands

| ST[1:0] |   | Status                   | Description                                 | SF[1:0]                  |   | Priority |

|---------|---|--------------------------|---------------------------------------------|--------------------------|---|----------|

| 0       | 0 | Device in Initialization | Device in initialization (ENDINIT not set)  | 0                        | 0 | 3        |

| 0       | 1 | Normal Mode              | Normal mode(ENDINIT set)                    | 0                        | 0 | 4        |

| 1       | 0 | Self-test                | Self-test(ST_CTRL[3:0] not equal to '0000') | 0                        | 0 | 2        |

| 1       | 1 | Internal Error Present   | Detailed Status Field                       | Detailed Status<br>Field |   | 1        |

#### 7.5.5.2 Detailed status field

The response to sensor data requests includes a detailed status field (SF[1:0]). The contents of the detailed status field is a representation of the device status at the rising edge of SS\_B for the previous SPI command.

Table 34. Detailed status bit field descriptions

| SF[1:0] |                              | Status Sources                                                                      | DEVSTAT State                                                                |

|---------|------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 0       | 0 CM_ERROR Temperature error |                                                                                     | Bit set in DSP_STAT Bit set in DEVSTAT2                                      |

| 0       | 1                            | User OTP memory error (UF2 or UF1) User R/W memory error (UF2) NXP OTP Memory error | U_OTP_ERR set in DEVSTAT2 U_RW_ERR set in DEVSTAT2 F_OTP_ERR set in DEVSTAT2 |

| 1       | 0                            | Test Mode active Supply error Reset error                                           | TESTMODE bit set in DEVSTAT Bit set in DEVSTAT1 DEVRES set                   |

| 1       | 1                            | MISO error<br>SPI error                                                             | Bit set in DEVSTAT3<br>N/A                                                   |

#### 7.5.5.3 SPI error

The following external SPI conditions result in a SPI error:

· SCLK is high when SS B is asserted.

XPS7550D4S

All information provided in this document is subject to legal disclaimers.

- The number of SCLK rising edges detected while SS B is asserted is not equal to 16.

- · SCLK is high when SS B is deasserted.

- · CRC error is detected (MOSI).

- A register write command to any register other than the DEVLOCK\_WR register is received while ENDINIT is set.

If a SPI error is detected, the device responds with the error response as described in <u>Section 7.5.5.2 "Detailed status field"</u> with the detailed status field set to "SPI Error" as defined in <u>Section 7.5.5.1 "Basic status field"</u>.

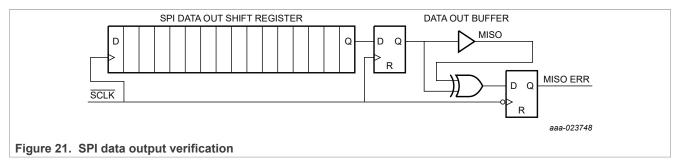

#### 7.5.5.4 SPI data output verification error

The device includes a function to verify the integrity of the data output to the MISO pin. The function compares the data transmitted on the MISO pin to the data intended to be transmitted. If any one bit does not match, a SPI MISO mismatch fault is detected and the MISO\_ERR flag in the DEVSTAT2 register is set.

If a valid sensor data request message is received during the SPI transfer with the MISO mismatch failure, the request is ignored and the device responds with the error response as described in <u>Section 7.5.5.2 "Detailed status field"</u> with the detailed status field set to "SPI Error" as defined in <u>Section 7.5.5.1 "Basic status field"</u> during the subsequent SPI message.

If a valid register write request message is received during the SPI transfer with the MISO mismatch failure, the register write is completed as requested, but the device responds with the error response as described in <a href="Section 7.5.5.2">Section 7.5.5.2</a> "Detailed status field" with the detailed status field set to "SPI Error" as defined in <a href="Section 7.5.5.1">Section 7.5.5.1</a> "Basic status field" during the subsequent SPI message.

If a valid register read request message is received during the SPI transfer with the MISO mismatch failure, the register read is ignored and the device responds with the error response as described in <a href="Section 7.5.5.2" "Detailed status field" with the detailed status field set to "SPI Error" as defined in <a href="Section 7.5.5.1" "Basic status field",">Section 7.5.5.1</a> "Basic status field", during the subsequent SPI message.

## 7.5.6 SPI timing diagram

## 7.6 User-accessible data array

A user-accessible data array allows each device to be customized. The array consists of a one time programmable (OTP) factory-programmable block, an OTP user-programmable block, and read-only registers for data and device status. The OTP blocks incorporate independent data verification. In order to perform the OTP, a custom platform is typically used prior to PCB assembly since the VPP voltage required is much higher than the nominal supply as shown in Table 103. See application note AN12727<sup>[3]</sup>.

Table 35. User-accessible data — sensor specific information

| Address       | Register          | Type <sup>['</sup> | 1]            |               |          | В               | it              |                |                 |          |

|---------------|-------------------|--------------------|---------------|---------------|----------|-----------------|-----------------|----------------|-----------------|----------|

|               |                   |                    | 7             | 6             | 5        | 4               | 3               | 2              | 1               | 0        |

| General d     | evice information |                    |               |               |          |                 |                 |                |                 |          |

| <u>00h</u>    | COUNT             | R                  |               |               |          | COUN            | IT[7:0]         |                |                 |          |

| <u>01h</u>    | DEVSTAT           | R                  | DSP_ERR       | reserved      | COMM_ERR | MEMTEMP_<br>ERR | SUPPLY_<br>ERR  | TESTMODE       | DEVRES          | DEVINIT  |

| <u>02h</u>    | DEVSTAT1          | R                  | VCCUV_<br>ERR | reserved      | reserved | reserved        | INTREGA_<br>ERR | INTREG_<br>ERR | INTREGF_<br>ERR | CONT_ERR |

| <u>03h</u>    | DEVSTAT2          | R                  | F_OTP_ERR     | U_OTP_<br>ERR | U_RW_ERR | U_W_<br>ACTIVE  | reserved        | TEMP0_<br>ERR  | reserved        | reserved |

| <u>04h</u>    | DEVSTAT3          | R                  | MISO_ERR      | reserved      | reserved | reserved        | reserved        | reserved       | reserved        | reserved |

| 05h to<br>0Dh | reserved          | R                  |               |               |          | rese            | rved            |                |                 |          |

| <u>0Eh</u>    | TEMPERATURE       | R                  |               |               |          | TEM             | P[7:0]          |                |                 |          |

| 0Fh           | reserved          | R                  |               |               |          | rese            | rved            |                |                 |          |

Table 35. User-accessible data — sensor specific information...continued

| Address            | Register            | Type <sup>[′</sup> | ]                |          |             | Е               | Bit              |                            |            |           |  |  |

|--------------------|---------------------|--------------------|------------------|----------|-------------|-----------------|------------------|----------------------------|------------|-----------|--|--|

|                    |                     |                    | 7                | 6        | 5           | 4               | 3                | 2                          | 1          | 0         |  |  |

| Communi            | cation information  |                    |                  |          |             |                 |                  |                            |            |           |  |  |

| <u>10h</u>         | DEVLOCK_WR          | R/W                | ENDINIT          | reserved | reserved    | reserved        | SUP_<br>ERR_DIS  | reserved                   | RESE       | T[1:0]    |  |  |

| <u>11h</u>         | WRITE_OTP_EN        | R/W                | UOTP_<br>WR_INIT |          | reserved    |                 | EX_<br>COMMTYPE  | EX_PADDR                   | UOTP_RE    | GION[1:0] |  |  |

| 12h to<br>13h      | reserved            | R/W                |                  |          |             | rese            | erved            |                            |            |           |  |  |

| <u>14h</u>         | UF_REGION_W         | R/W                |                  | REGION_  | LOAD[3:0]   |                 | 0                | 0 0 0                      |            |           |  |  |

| <u>15h</u>         | UF_REGION_R         | R                  |                  | REGION_A | ACTIVE[3:0] |                 | 0                | 0 0 0                      |            |           |  |  |

| 16h to<br>19h      | reserved            | UF2                |                  |          |             | rese            | erved            |                            |            |           |  |  |

| <u>1Ah</u>         | SOURCEID_0          | UF2                | SID0_EN          |          | reserved    |                 |                  | SOURCE                     | EID_0[3:0] |           |  |  |

| <u>1Bh</u>         | SOURCEID_1          | UF2                | SID1_EN          |          | reserved    |                 |                  | SOURCE                     | EID_1[3:0] |           |  |  |

| 1Ch to<br>3Ch      | reserved            | UF2                |                  |          |             | rese            | rved             |                            |            |           |  |  |

| <u>3Dh</u>         | SPI_CFG             | UF2                | reserved         | DATASIZE | SPI_CRC     | _LEN[1:0]       |                  | SPICROS                    | SEED[3:0]  |           |  |  |

| <u>3Eh</u>         | WHO_AM_I            | UF2                |                  |          |             | WHO_A           | M_I[7:0]         |                            |            |           |  |  |

| <u>3Fh</u>         | I2C_ADDRESS         | UF2                |                  |          |             | I2C_ADD         | RESS[7:0]        |                            |            |           |  |  |

| Sensor sp          | pecific information |                    |                  |          |             |                 |                  |                            |            |           |  |  |

| <u>40h</u>         | DSP_CFG_U1          | UF2                |                  | LPF      | [3:0]       |                 | reserved         | reserved                   | reserved   | reserved  |  |  |

| 41h                | reserved            | UF2                |                  |          |             | rese            | rved             |                            |            |           |  |  |

| <u>42h</u>         | DSP_CFG_U3          | UF2                | reserved         | DATATY   | PE0[1:0]    | reserved        | DATATY           | DATATYPE1[1:0] reserved re |            |           |  |  |

| <u>43h</u>         | DSP_CFG_U4          | UF2                | reserved         | reserved | reserved    | reserved        | reserved         | INT_OUT                    | reserved   | reserved  |  |  |