#### **APPLICATION NOTE**

# Application information for TDA6107JF/07AJF/08JF/08AJF triple video output amplifiers

AN10227-01

Version 1.2 July 2004

#### **ABSTRACT**

This report gives a description of the application aspects of the TDA6107JF/07AJF/08JF/08AJF

© Philips Electronics N.V. 2004

All rights are reserved. Reproduction in whole or in part is prohibited without the prior consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

#### **APPLICATION NOTE**

# Application information for TDA6107JF/07AJF/08JF/08AJF triple video output amplifiers

AN10227-01

Authors: Roland Peters Pieter van Oosten

Systems & Applications, Innovation Center Nijmegen, Philips Semiconductors, Consumer Businesses

#### Keywords

Triple video amplifier

Black current stabilisation

Robust against flashover

Very simple application

Fixed gain

Date: July 2004

#### **Summary**

In this application note you can find an application description of the triple video output amplifiers with the type numbers TDA6107JF, TDA6107AJF, TDA6108JF and TDA6108AJF. All types include three video output amplifiers in a DBS9MPF package, version SOT111-1. The types are all functional the same, but the bandwidth level and gain level is different. A description of the differences between the types is given. Furthermore the video amplifiers are provided with a black current measurement output for automatic black current stabilisation. An optimal application and PCB-layout for flash protection is given.

#### **TABLE OF CONTENTS:**

| 1.        | INTRODUCTION                                                 | 7  |

|-----------|--------------------------------------------------------------|----|

| 2.        | FUNCTIONAL PIN DESCRIPTION.                                  | 8  |

| 2.1       | Input pins 1, 2 and 3                                        | 8  |

| 2.2       | Pin 4                                                        | 8  |

| 2.3       | Pin 5                                                        | 9  |

| 2.4       | Pin 6                                                        | 10 |

| 2.5       | Output pins 7, 8 and 9                                       | 10 |

| 3.        | DISSIPATION AND HEATSINK CALCULATION                         | 11 |

| 3.1       | Dissipation                                                  | 11 |

| 3.2       | Heatsink calculation                                         | 12 |

| 4.        | FLASHOVER PROTECTION                                         | 14 |

| 4.1       | Checklist TDA6107JF / 07AJF for optimal flashover robustness | 15 |

| 4.2       | Checklist TDA6108JF / 08AJF for optimal flashover robustness | 19 |

| 5.<br>BOA | THE TDA6107JF / 07AJF AND TDA6108JF / 08AJF REFERENCE / DEMO | 23 |

## TDA6107JF/07AJF/08JF/08AJF Triple video output amplifiers

## Application Note AN10227-01

#### **LIST OF FIGURES:**

| Figure 1: Internal circuitry                                                   | 8  |

|--------------------------------------------------------------------------------|----|

| Figure 2: Switch off behaviour                                                 |    |

| Figure 3: Thermal resistance                                                   | 12 |

| Figure 4: Power dissipation as a function of the input frequency               | 13 |

| Figure 5: Grounding of aquadag and CRT board                                   |    |

| Figure 6: Application diagram of the TDA6107JF/07AJF                           |    |

| Figure 7: Optimal CRT PCB-layout with TDA6107JF/07AJF                          |    |

| Figure 8: Application diagram TDA6108JF/08AJF                                  |    |

| Figure 9: Optimal CRT PCB-layout with TDA6108JF/08AJF                          |    |

| Figure 10: Application diagram of the TDA6107JF / 07AJF reference / demo board |    |

| Figure 11: TDA6107JF / 07AJF reference / demo board layout                     |    |

| Figure 12: Components TDA6107JF / 07AJF reference / demo board                 |    |

| Figure 13: Application diagram of the TDA6108JF / 08AJF reference / demo board |    |

| Figure 14: TDA6108JF / 08AJF reference / demo board layout                     |    |

| Figure 15: Components TDA6108JF / 08AJF reference / demo board                 |    |

|                                                                                |    |

#### 1. INTRODUCTION

This application note provides a design guide for successful implementation and design-in of the TDA6107JF/07AJF/08JF/08AJF family. It is meant as a complement of the data sheet, and should not be used without the specific datasheet of the video amplifier that is being designed in.

The TDA6107JF/07AJF/08JF/08AJF family consists of a complete range of triple video amplifiers to cover the low and midrange TV sets. All types include three video output amplifiers in a DBS9MPF package, version SOT111-1.

The features of these amplifiers are:

- Single package for three amplifiers

- One supply voltage

- Fixed gain (less spread and saving external resistors)

- Black current stabilisation output

- Internal flash protection

- Low power dissipation

- Internal thermal protection

Table 1 gives an overview of the bandwidth and gain factors.

| Туре       | Typical Gain | Large signal bandwidth |

|------------|--------------|------------------------|

|            |              |                        |

| TDA6107JF  | 51           | 4.5 MHz                |

| TDA6107AJF | 81           | 4.5 MHz                |

| TDA6108JF  | 51           | 8.0 MHz                |

| TDA6108AJF | 81           | 8.0 MHz                |

Table 1

#### 2. FUNCTIONAL PIN DESCRIPTION.

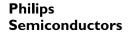

The internal circuitry of the video amplifier can be seen as an operational amplifier with negative feedback, see Figure 1 below.

Figure 1: Internal circuitry

#### 2.1 Input pins 1, 2 and 3.

These pins are the inputs of channel 1, 2 and 3.

The internal resistor Ri is given in the datasheet, and can be used to calculate Ra and Rf. This is normally not useful, however if adding external resistors for EMC reasons or suppressing interference it can be useful.

The gain and the gain difference depend on the ratio between Rf and Ri, so if the value of Ri changes due to adding external resistors, the gain will change.

The new gain can be calculated with the following equation.

$$G_{NEW} = \frac{G_{SPEC} * R_{ISPEC}}{R_{ISPEC} + R_{S}}$$

Where:

$G_{NEW}$  is the new gain.

$G_{\text{SPEC}}$  is the typical gain mentioned in the datasheet.

R<sub>ISPEC</sub> is the typical input resistance as mentioned in the datasheet.

R<sub>S</sub> is the added series resistance.

We do not recommend to add these extra series resistance, because there will be a bigger spread in gain between products due to the spread in Ri.

Furthermore adding extra series resistance makes the step response worse. This means that the ringing and overshoot will increase.

#### 2.2 Pin 4.

This pin is the ground connection of the amplifier. It should be directly connected to the small signal GND, with a trace as short as possible (see chapter 4).

#### 2.3 Pin 5.

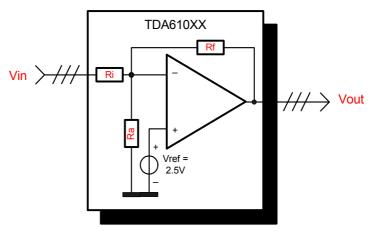

Pin 5 is the black current measurement output of the amplifier. The current flowing out of this pin is equivalent to the sum of the currents flowing in the cathodes of the CRT (between certain limits). This output is intended to be used in the cathode calibration loop (black current stabilization), but can also be used for discharging the CRT after set switch-off (except the TDA6108JF). This pin can be directly connected to the TV-signal processor, but for stability it is allowed to add a series resistance and a capacitor to ground. When calculating this RC combination, keep in mind that the output must be stable within 39µs (due to timing of the TV-signal processor) after start of the measurement line. Another possibility to minimize disturbances is to shield the return wire and to embed the I<sub>om</sub> track in a ground plane on the PCB layout.

The maximum average current for the TDA6108AJF must be limited to 5.6mA; therefore a series resistance must be used. An internal zener diode is connected to the  $I_{om}$  pin, and limits the voltage of this output between 6V and 10V. By means of this data, the minimal value of the resistor can be calculated with:

$$R \min = \frac{Vomclamp \max - Vbias}{Iom \max}$$

Where:

V<sub>OMCLAMPmax</sub> is the maximal clamp voltage of the internal zener diode

$V_{\text{BIAS}}$  is the minimal bias voltage of the  $I_{\text{om}}$  input of the TV-signal processor

lom<sub>MAX</sub> is the maximal allowed average current of the RGB amplifier

For the TDA110XXH/TDA120XXH family (UOCIII series) this results in a minimal resistance of:

$$R \min = \frac{10V - 3V}{5.6mA} = 1250\Omega$$

The maximal value of this resistor is determined by the TV-signal processor. If the resistor value is chosen too high, the feedback current will be influenced.

As the voltage drop across the resistor will be too high and thus the zener diode will conduct and therefore a part of the current will flow through the zener diode instead of into the TV-signal processor. The maximal value can be calculated by:

$$R \max = \frac{Vomclamp \min - Vbias}{I_{\max}}$$

Where:

$V_{\text{OMCLAMPmin}}$  is the minimal clamp voltage of the internal zener diode

V<sub>BIAS</sub> is the minimal bias voltage of the I<sub>om</sub> input of the TV-signal processor

I<sub>MAX</sub> is the maximal current running into the TV-signal processor during discharge or during a

measuring line (if no discharge function is used).

For the TDA110XXH/TDA120XXH family (UOCIII series) this results in a maximal resistance of:

$$R \max = \frac{6-3V}{1mA} = 3k\Omega$$

During a transition of the video signal, there will be some voltage spikes on the I<sub>om</sub> output. These spikes are a result of fast charging and discharging parasitic capacitance. The amplitude of the spikes is limited to the clamp voltage of the internal zener diode and will cause no problems.

#### 2.4 Pin 6.

This pin is the  $V_{DD}$  connection, it must be decoupled to ground with a capacitor and an electrolytic capacitor to ground, to protect the video amplifier for flashover, see the chapter 4

#### 2.5 Output pins 7, 8 and 9

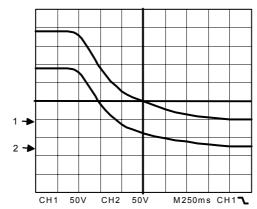

These are the outputs of channel 3, 2 and 1, with a defined switch-off behavior.

These pins stay under control of the input voltage even for low values of  $V_{DD}$ . This means that the output voltage  $V_{OC}$  follows the discharge curve of  $V_{DD}$  when the TV set is switched off. See Figure 2: Switch off behaviour.

Figure 2: Switch off behaviour

#### 3. DISSIPATION AND HEATSINK CALCULATION

#### 3.1 Dissipation

The total amount of dissipation in the triple video amplifiers consists of a sum of two powers. The first part is the static dissipation, which is the result of the quiescent current and can be calculated with:

$$P_{STAT} = V_{DD} * I_{DD} + 3 * (V_{OCdc} * I_{OCdc})$$

Where:

$V_{DD}$  is the supply voltage.  $I_{DD}$  is the supply current.

$V_{\text{OCdc}}$  is the value of the cathode offset. I<sub>OCdc</sub> is the value of the dc output current.

The second part is the dynamic dissipation, which is a result of continuously switching of the internal circuitry and thus charging and discharging of on-chip parasitic and load capacitance. For a sinusoidal signal, it can be calculated with:

$$P_{DYN} = 3* \left(V_{DD}*C_{TOT}*f_{IN}*V_{OCpp}*\delta*\frac{1}{\sqrt{1+rac{f_{IN}}{B_L}}}\right)$$

Where:

$V_{DD}$  is the supply voltage.

$C_{\text{TOT}}$  is the sum of the internal- and load capacitance.

f<sub>IN</sub> Frequency of the input signal.

$V_{\text{OCpp}}$  Peak to peak AC component of the output signal.

$\delta$  Non-blanking duty cycle.

B<sub>L</sub> Large signal bandwidth of the video amplifier.

This formula however is not representative for a real condition in a TV set. A nominal TV picture consists of a complex variety of signals. If we would use these formulas to calculate a heatsink, the heatsink would be far too big and too expensive. So to calculate a proper heatsink, it is better to see what the video amplifier dissipates in a worst-case condition.

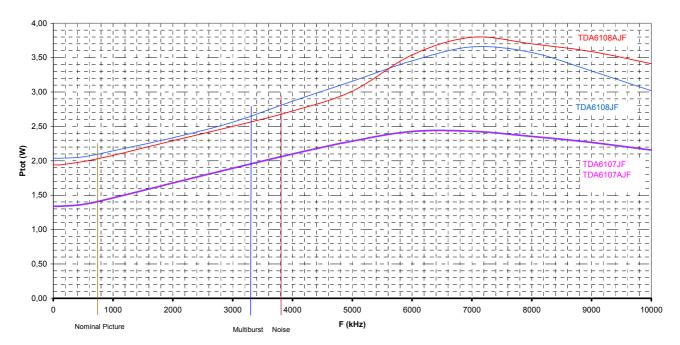

Figure 4 shows the power dissipation as a function of the input frequency. The test conditions for these graphs are given in Table 3: Test conditions.

All video amplifiers are equipped with an internal thermal protection. This circuit gives a decrease of the slew rate if the temperature of the die is higher than 130°C. This prevents thermal ageing and reduces the necessary heatsink size. Taking this into account, the worst-case condition whereby the slew rate should not be influenced is a multiburst video signal. So the heatsink should be calculated for this condition.

#### 3.2 Heatsink calculation

How the heatsink can be calculated is shown underneath.

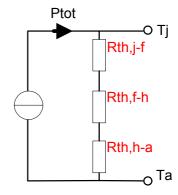

$$R_{TH, H-A} = \frac{T_{JMAX} - T_A}{P_{TOT}} - (R_{TH, J-F} + R_{TH, F-H})$$

Where:

$\begin{array}{lll} R_{TH,H-A} & \text{is the thermal resistance from heatsink to ambient.} \\ R_{TH,J-F} & \text{is the thermal resistance from junction to fin.} \\ R_{TH,F-H} & \text{is the thermal resistance from fin to heatsink.} \\ T_{JMAX} & \text{is the maximum junction temperature.} \end{array}$

T<sub>A</sub> is the ambient temperature in a TV set.

$P_{TOT}$  is the total of dissipated power.

Figure 3: Thermal resistance

The value for  $R_{TH,J-F}$  can be found in the datasheet, which is 11K/W for the DBS9MPF (SOT111-1) package. The value for  $R_{TH,F-H}$  depends on the mounting method and will be under normal conditions about 0.5K/W.

$T_{\text{JMAX}}$  is the temperature where the internal thermal protection starts to operate, and is approximately 130°C. The maximum ambient temperature in a TV set can be about 65°C, and  $P_{\text{TOT}}$  can be found in Figure 4.

Using this equation for the TDA6108AJF, this would result in a heatsink with a thermal resistance of at least 13.9K/W. The power curves given in Figure 4, are typical values, considering this, we should subtract 2K/W because of the variation in power dissipation. To minimise the dissipated power, it is advised to use the supply voltage  $V_{DD}$  as low as possible.

Table 2 gives a summery for the recommended heatsink values.

| Amplifier type:      | Power (multiburst) | Calculated heatsink value |

|----------------------|--------------------|---------------------------|

| TDA6107JF/TDA6107AJF | 1.9W               | 21.5 K/W                  |

| TDA6108JF/TDA6108AJF | 2.56W              | 12 K/W                    |

Table 2

Typical performance characteristics.

Table 3: Test conditions

| $V_{DD} = 200V$                | $V_{\rm OCdc} = 100V$ | δ=0.8            |

|--------------------------------|-----------------------|------------------|

| Туре                           | $V_{OCpp}$            | $C_{TOT}$        |

| TDA6107JF/AJF<br>TDA6108JF/AJF | 100<br>100            | 4.5 pF<br>5.3 pF |

#### P=f(Fsin) (80% because of Fly Back)

Figure 4: Power dissipation as a function of the input frequency

#### 4. FLASHOVER PROTECTION

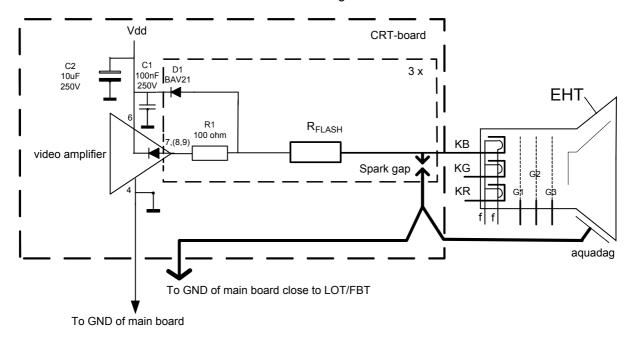

A picture tube has generally several high voltage discharges (flashovers) in its lifetime. During the flashovers, a high voltage will be present on the cathodes. The video amplifier must be protected from these flashovers. For optimal flashover protection the grounding wire from aquadag to CRT-board and from CRT-board to main board must be connected like in Figure 5 below.

Figure 5: Grounding of aquadag and CRT board.

The TDA6107JF / 07AJF does not need an external flash protection, when  $R_{\text{FLASH}}$  is larger than 1k. The TDA6108JF / 08AJF always needs external flash protection to protect against flashovers. The external flash protection consists of an external diode D1 and external resistor R1. The diode clamps the output voltage to the  $V_{\text{DD}}$ . To limit the diode current an external surge resistor (high voltage resistor)  $R_{\text{FLASH}}$  must be used together with a 2kV spark gap. A more detailed description about the external flash protection is given in the checklist in the next paragraph: 4.1.

#### 4.1 Checklist TDA6107JF / 07AJF for optimal flashover robustness

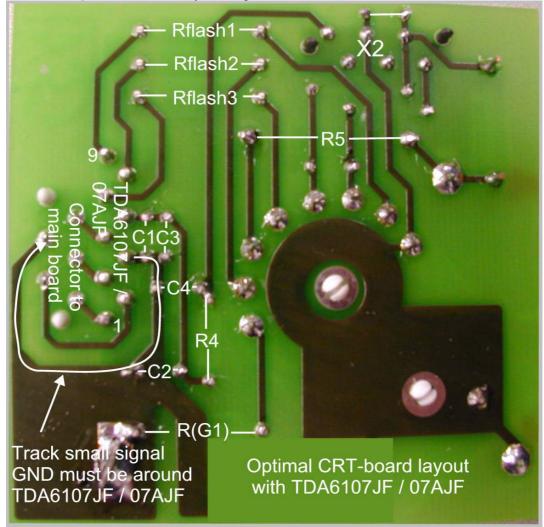

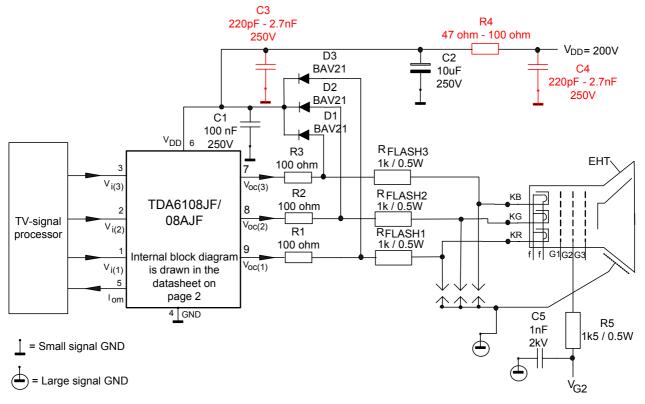

Figure 6: Application diagram of the TDA6107JF/07AJF

#### **Checklist:**

|    | TDA6107JF / 07AJF                                                                                                                                             | Recommended value | Explanation                                                                                          |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                               | / type            |                                                                                                      |

|    | Grounding of the CRT PCB-I                                                                                                                                    | ayout             | <del>,</del>                                                                                         |

| 1. | On the CRT PCB-layout the                                                                                                                                     |                   | Prevents that large flashover voltage /                                                              |

|    | large signal GND must be                                                                                                                                      |                   | current peaks can directly flow through the                                                          |

|    | isolated from the small signal                                                                                                                                |                   | small signal GND.                                                                                    |

|    | GND. So pin 4 GND of the                                                                                                                                      |                   | -                                                                                                    |

|    | TDA6118JF must not be                                                                                                                                         |                   |                                                                                                      |

|    | connected directly to the                                                                                                                                     |                   |                                                                                                      |

|    | spark gap GND (focus, G2                                                                                                                                      |                   |                                                                                                      |

|    | and cathodes) of the CRT-                                                                                                                                     |                   |                                                                                                      |

|    | socket. See Figure 7.                                                                                                                                         |                   |                                                                                                      |

| 2. | It is also strongly recommended to place no components (capacitors, resistors and coils) between the small signal GND and the large signal GND. See Figure 7. |                   | Prevents that large flashover voltage / current peaks can directly flow through the small signal GND |

| 3. | Ground loops in the small signal GND must be avoided. So pin 4 GND must have one connection to the connector to the main board. See Figure 7. |                                                                                                                        | Ground loops could reveal in large voltage peaks due to long tracks. V = L*di/dt generated during a flashover                                         |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. | Small signal ground track<br>must be around the<br>TDA6107JF / 07AJF. See<br>Figure 7.                                                        |                                                                                                                        | To avoid current / voltage peaks at pin 4 GND during a flashover.                                                                                     |

|    | External protection compon                                                                                                                    | ents, decoupling circuit                                                                                               | S                                                                                                                                                     |

| 5. | High frequency decoupling capacitor, C1                                                                                                       | 100nF / 250V                                                                                                           | C1 has to reduce fast large voltage peaks<br>between pin 6 $V_{DD}$ and pin 4 GND due to V<br>= L*di/dt. (See points x + x for optimal PCB<br>layout) |

| 6. | Low frequency decoupling capacitor, C2                                                                                                        | <ul> <li>4.7uF / 250V for ≤21 inch picture tube size</li> <li>10uF / 250V for &gt;21 inch picture tube size</li> </ul> | Low frequency current peaks from a flashover flows via D1, D2 and D3 into C2.                                                                         |

| 7. | High frequency decoupling capacitor, C3                                                                                                       | 220pF - 2.7nF / 250V                                                                                                   | C3 has to reduce fast large voltage peaks between pin 6 V <sub>DD</sub> and pin 4 GND due to V = L*di/dt.                                             |

| 8. | Series resistor, R4                                                                                                                           | 47Ω - 100Ω / 0.25W                                                                                                     | In combination with C3 and C4 for optimal flash robustness.                                                                                           |

| 9. | High frequency decoupling capacitor, C4                                                                                                       | 220pF - 2.7nF / 250V                                                                                                   | C4 has to reduce fast large voltage peaks between pin 6 V <sub>DD</sub> and pin 4 GND due to V = L*di/dt.                                             |

|    | All external capacitors of the TDA6107JF / 07AJF application must be grounded to the <b>small signal GND</b>                                  |                                                                                                                        |                                                                                                                                                       |

The value of C3, C4 and R4 depend on the layout of the CRT-board. During a flashtest can be checked which values give the lowest voltage peaks between pin 6  $V_{DD}$  and pin 4 GND. These voltage peaks can be measured with a digital oscilloscope with probes and grounding as close as possible to pin 6  $V_{DD}$  and pin 4 GND. A special provision can be made on the probe to be close to the pins. It is very important that the grounding wire of the probe is short for not picking up spikes in the GND.

|     | External protection comp                                           | onents, diodes and resisto                                                                                                               | rs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10. | Flash resistor, R <sub>FLASH</sub> => Always needed in application | 1.5kΩ / 0.5W surge resistor (high voltage resistor). R <sub>FLASH</sub> must be capable of handling large peak voltages from a flashover | <ul> <li>Limits flashover current peaks</li> <li>When the value is larger than 1.5kΩ, the bandwidth will be reduced.</li> <li>When the value is smaller than 1.5kΩ, larger than 3A flash current peaks can be expected and external flash protection (D1 + R1) must be used.</li> <li>When the value ≥ 1.5kΩ, a maximum value of 3A flash current peaks can be expected and the external flash protection (D1 + R1) is NOT needed. The internal flash diodes are capable of handling a maximum value of 3A flash current peaks.</li> </ul> |

| 11. | Diode, D1, D2 and D3<br>=> Only needed when the          | BAV21 or equivalent.<br>D1 must have a fast | D1, D2 and D3 clamp the output to the $V_{DD}$ supply during a flashover.       |

|-----|----------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|

|     | value of R <sub>FLASH</sub> is lower than                | transient response,                         | supply saming a massic section                                                  |

|     | 1.5kΩ                                                    | low shunt capacitance and capable of        |                                                                                 |

|     |                                                          | handling large peak                         |                                                                                 |

|     |                                                          | currents from a flashover.                  |                                                                                 |

| 12. | Resistor, R1, R2 and R3                                  | 100Ω / 0.25W                                | Limits current into video amplifier                                             |

|     | => Only needed when the                                  |                                             | , , , , , , , , , , , , , , , , , , ,                                           |

|     | value of R <sub>FLASH</sub> is lower than                |                                             |                                                                                 |

| 13. | 1.5kΩ Resistor, R5                                       | 1.5kΩ / 0.5W surge                          | Limits flashover current peaks on the CRT-                                      |

| '   | 1.00.0.01, 1.00                                          | resistor (high voltage                      | board                                                                           |

|     |                                                          | resistor). R5 must be                       |                                                                                 |

|     |                                                          | capable of handling large peak voltages     |                                                                                 |

|     |                                                          | from a flashover                            |                                                                                 |

|     | Optimal PCB-layout to have                               |                                             |                                                                                 |

| 14. | If D1, D2 and D3 are needed,                             | <5mm                                        | A small discharge loop. The track between                                       |

|     | the cathodes of D1, D2 and D3 must be close to C1 in the |                                             | diodes and capacitor must be short to avoid high voltages V = L*di/dt generated |

|     | layout. See Figure 7 below.                              |                                             | during a flashover.                                                             |

| 15. | C1 must be as close as                                   | <5mm                                        | Prevent that large flashover voltage /                                          |

|     | possible to pin 6 V <sub>DD</sub> and pin                |                                             | current peaks can directly flow through the                                     |

|     | 4 GND of the video amplifier. See Figure 7 below.        |                                             | small signal GND.                                                               |

| 16. | Distance of G2, G1, R, G and                             | > 3 mm                                      | Prevent arcing during flash over.                                               |

|     | B copper tracks to adjacent                              |                                             |                                                                                 |

| 17. | tracks G2 CRT pins must have 2                           |                                             | Prevent arcing during flash over.                                               |

| ''' | slots cut on the PCB to                                  |                                             | Trevent arong daming hadri ever.                                                |

|     | increase the distance from                               |                                             |                                                                                 |

| 18. | the adjacent R and B pins.  No copper track in between   |                                             | Prevent arcing during flash over.                                               |

| 10. | CRT pins.                                                |                                             |                                                                                 |

| 19. | No sharp edges on the copper track.                      |                                             | Prevent arcing during flash over.                                               |

| 20. | Large signal GND and (if                                 | > 2mm                                       | Prevent arcing during flash over.                                               |

|     | used) EHT info track distance                            |                                             |                                                                                 |

|     | must be 2mm from all other tracks.                       |                                             |                                                                                 |

| 21. | CRT wire between aquadag                                 |                                             | A small discharge loop during flashover.                                        |

|     | layer and CRT-board must                                 |                                             | g , , , , , , , , , , , , , , , , , , ,                                         |

| 20  | be as short as possible.                                 |                                             | Lauring adams a disabage la sa dusis s                                          |

| 22. | CRT wire between aquadag layer and CRT-board must        |                                             | Low impedance discharge loop during flashover.                                  |

|     | not be too thin.                                         |                                             | indono voi.                                                                     |

Figure 7 shows the optimal CRT PCB-layout for good flashover robustness.

Figure 7: Optimal CRT PCB-layout with TDA6107JF/07AJF

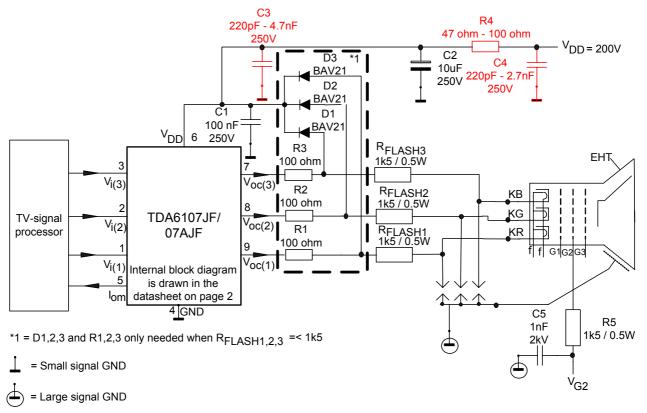

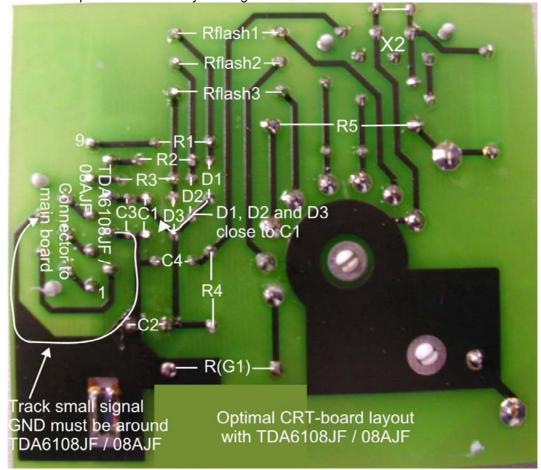

#### 4.2 Checklist TDA6108JF / 08AJF for optimal flashover robustness

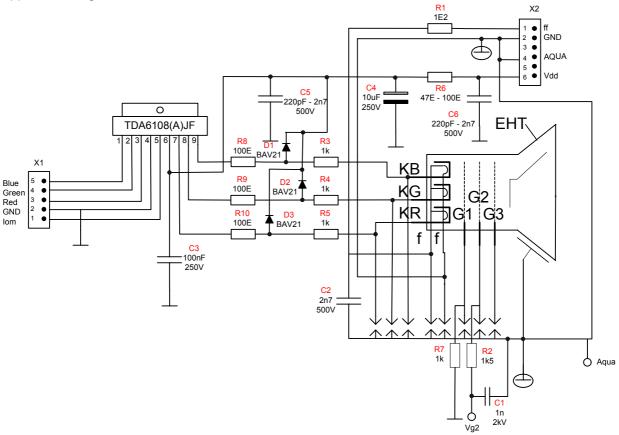

Figure 8: Application diagram TDA6108JF/08AJF

#### **Checklist:**

| Onc | Checklist:                                                                                                                                                                                                                                 |                   |                                                                                                               |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|--|

|     | TDA6108JF / 08AJF                                                                                                                                                                                                                          | Recommended value | Explanation                                                                                                   |  |

|     |                                                                                                                                                                                                                                            | / type            |                                                                                                               |  |

|     | Grounding of the CRT PCB-I                                                                                                                                                                                                                 | ayout             |                                                                                                               |  |

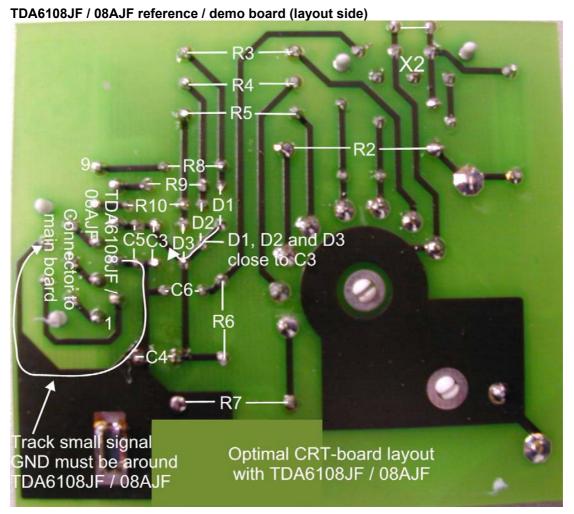

| 1.  | On the CRT PCB-layout the large signal GND must be isolated from the small signal GND. So pin 4 GND of the TDA6108JF / 08AJF must not be connected directly to the spark gap GND (focus, G2 and cathodes) of the CRT-socket. See Figure 9. |                   | Prevents that large flashover voltage / current peaks can directly flow through the small signal GND.         |  |

| 2.  | It is also strongly recommended to place no components (capacitors, resistors and coils) between the small signal GND and the large signal GND. See Figure 9.                                                                              |                   | Prevents that large flashover voltage / current peaks can directly flow through the small signal GND          |  |

| 3.  | Ground loops in the small signal GND must be avoided. So pin 4 GND must have one connection to the connector to the main board. See Figure 9.                                                                                              |                   | Ground loops could reveal in large voltage peaks due to long tracks. V = L*di/dt generated during a flashover |  |

| 4. | Small signal ground track<br>must be around the<br>TDA6108JF / 08AJF. See<br>Figure 9. |                                                                                                                                                        | To avoid current / voltage peaks at pin 4 GND during a flashover.                                                                                       |

|----|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | External protection compone                                                            | ents, decoupling circuits                                                                                                                              | <b>;</b>                                                                                                                                                |

| 5. | High frequency decoupling capacitor, C1                                                | 100nF / 250V                                                                                                                                           | C1 has to reduce fast large voltage peaks<br>between pin 6 $V_{DD}$ and pin 4 GND due to $V$<br>= L*di/dt. (See points x + x for optimal PCB<br>layout) |

| 6. | Low frequency decoupling capacitor, C2                                                 | <ul> <li>4.7uF / 250V for         ≤21 inch picture         tube size</li> <li>10uF / 250V for         &gt;21 inch picture         tube size</li> </ul> | Low frequency current peaks from a flashover flows via D1, D2 and D3 into C2.                                                                           |

| 7. | High frequency decoupling capacitor, C3                                                | 220pF – 2.7nF / 250V                                                                                                                                   | C3 has to reduce fast large voltage peaks between pin 6 V <sub>DD</sub> and pin 4 GND due to V = L*di/dt.                                               |

| 8. | Series resistor, R4                                                                    | 47Ω - 100Ω / 0.25W                                                                                                                                     | In combination with C3 and C4 for optimal flash robustness.                                                                                             |

| 9. | High frequency decoupling capacitor, C4                                                | 220pF – 2.7nF / 250V                                                                                                                                   | C4 has to reduce fast large voltage peaks between pin 6 V <sub>DD</sub> and pin 4 GND due to V = L*di/dt.                                               |

|    | All external capacitors of the T <b>GND</b>                                            | DA6108JF / 08AJF applic                                                                                                                                | ation must be grounded to the small signal                                                                                                              |

The value of C3, C4 and R4 depend on the layout of the CRT-board. During a flashtest can be checked which values give the lowest voltage peaks between pin 6  $V_{DD}$  and pin 4 GND. These voltage peaks can be measured with a digital oscilloscope with probes and grounding as close as possible to pin 6  $V_{DD}$  and pin 4 GND. A special provision can be made on the probe to be close to the pins. It is very important that the grounding wire of the probe is short for not picking up spikes in the GND.

|     | External protection components, diodes and resistors               |                                                                                                                                                                    |                                                                                                                                                                                                                                |  |

|-----|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10. | Flash resistor, R <sub>FLASH</sub> => Always needed in application | 1kΩ / 0.5W low ohmic<br>surge resistor (high<br>voltage resistor).<br>R <sub>FLASH</sub> must be<br>capable of handling<br>large peak voltages<br>from a flashover | <ul> <li>Limits flashover current peaks</li> <li>When the value is larger than 1kΩ, the bandwidth will be reduced.</li> <li>When the value is smaller than 1kΩ, larger than 5A flash current peaks can be expected.</li> </ul> |  |

| 11. | Diode, D1, D2 and D3<br>=> Always needed in<br>application         | BAV21 or equivalent. D1 must have a fast transient response, low shunt capacitance and capable of handling large peak currents from a flashover.                   | D1, D2 and D3 clamp the output to the V <sub>DD</sub> supply during a flashover.                                                                                                                                               |  |

| 12. | Resistor, R1, R2 and R3 => Always needed in application            | 100Ω / 0.25W                                                                                                                                                       | Limits flashover current peaks on the CRT-board                                                                                                                                                                                |  |

| 13. | Resistor, R5                                                       | 1.5kΩ / 0.5W surge resistor (high voltage resistor). R5 must be capable of handling large peak voltages from a flashover                                           | Limits flashover current peaks on the CRT-board                                                                                                                                                                                |  |

|     | Optimal PCB-layout to have optimal robustness                                                                      |        |                                                                                                                                               |

|-----|--------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 14. | If D1, D2 and D3 are needed, the cathodes of D1, D2 and D3 must be close to C1 in the layout. See Figure 9 below.  | <5mm   | A small discharge loop. The track between diodes and capacitor must be short to avoid high voltages V = L*di/dt generated during a flashover. |

| 15. | C1 must be as close as possible to pin 6 V <sub>DD</sub> and pin 4 GND of the video amplifier. See Figure 9 below. | <5mm   | Prevent that large flashover voltage / current peaks can directly flow through the small signal GND.                                          |

| 16. | Distance of G2, G1, R, G and B copper tracks to adjacent tracks                                                    | > 3 mm | Prevent arcing during flash over.                                                                                                             |

| 17. | G2 CRT pins must have 2 slots cut on the PCB to increase the distance from the adjacent R and B pins.              |        | Prevent arcing during flash over.                                                                                                             |

| 18. | No copper track in between CRT pins.                                                                               |        | Prevent arcing during flash over.                                                                                                             |

| 19. | No sharp edges on the copper track.                                                                                |        | Prevent arcing during flash over.                                                                                                             |

| 20. | Large signal GND and (if used) EHT info track distance must be 2mm from all other tracks.                          | > 2mm  | Prevent arcing during flash over.                                                                                                             |

| 21. | CRT wire between aquadag layer and CRT-board must be as short as possible.                                         |        | A small discharge loop during flashover.                                                                                                      |

| 22. | CRT wire between aquadag layer and CRT-board must not be too thin.                                                 |        | Low impedance discharge loop during flashover.                                                                                                |

Figure 9 shows the optimal CRT PCB-layout for good flashover robustness.

Figure 9: Optimal CRT PCB-layout with TDA6108JF/08AJF

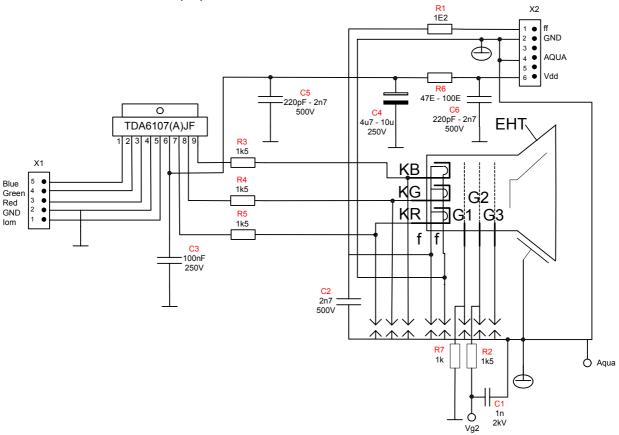

### 5. THE TDA6107JF / 07AJF AND TDA6108JF / 08AJF REFERENCE / DEMO BOARD

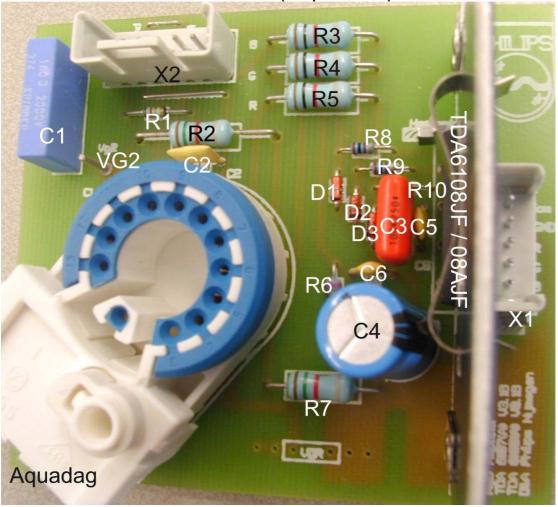

The TDA6107JF / 07AJF reference board is shown in Figure 11 and Figure 12. The TDA6108JF / 08AJF has its own reference / demo board and is shown in Figure 14 and Figure 15. These boards are meant for evaluation and demonstration purposes.

Figure 10: Application diagram of the TDA6107JF / 07AJF reference / demo board

When the TDA6107JF / 07AJF is used with **1k5** flash resistor (R3, R4, R5), the external flash diodes are **not** needed. If the TDA6107JF / 07AJF is used with **1k** flash resistors, external flash diodes +  $100\Omega$  resistors must be used. See for a detailed description section 4.1. For the TDA6107JF / 07AJF with external flash protection, the TDA6108JF / 08AJF reference / demo must be used.

G1 is connected to the **small** signal GND via a 1k flash resistor.

TDA6107JF / 07AJF reference / demo board (layout side)

R3

R4

R5

R1

R2

R7

Track small signal GND must be around TDA6107JF / 07AJF

R7

R7

R7

R7

R7

R7

Connector of the control of the control

Figure 11: TDA6107JF / 07AJF reference / demo board layout

This reference / demo board has an option to use the aquadag ground for the EHT info. This can be done by leaving out the jumper wire above connector X2. Then the aquadag ground is isolated from the large signal ground (heater and VG2 decoupling capacitor).

TDA6107JF / 07AJF reference / demo board (component side)

X2

R1

R2

R2

C1

VG2

C2

X1

C6

R7

Aquadag

Figure 12: Components TDA6107JF / 07AJF reference / demo board

On this TDA6107JF / 07AJF reference / demo board a 15.2 K/W heatsink is mounted, however a smaller heatsink of 21.5K/W would be sufficient for the TDA6107JF / 07AJF. See section: 3.2

Application diagram of the TDA6108JF / 08AJF reference / demo board:

Figure 13: Application diagram of the TDA6108JF / 08AJF reference / demo board

External flash diodes must always be used with the TDA6108JF / 08AJF.

G1 is connected to the **small** signal GND via a 1k flash resistor.

Figure 14: TDA6108JF / 08AJF reference / demo board layout

This reference / demo board has an option to use the aquadag ground for the EHT info. This can be done by leaving out the jumper wire above connector X2. Then the aquadag ground is isolated from the large signal ground (heater and VG2 decoupling capacitor).

TDA6108JF / 08AJF reference / demo board (component side)

Figure 15: Components TDA6108JF / 08AJF reference / demo board

On this TDA6108JF / 08AJF reference / demo board a 12 K/W heatsink is mounted, which is sufficient for the TDA6108JF / 08AJF. See section: 3.2.

### Philips Semiconductors – a worldwide company

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2002

SCB74

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Let's make things better.