Hello, welcome to this presentation of the low power timer, or LPTMR, module for Kinetis MCUs. In this session you'll learn about the LPTMR, it's main features and the application benefits of leveraging this function.

In this presentation, we'll cover:

- An overview of the module

- On-chip interconnections and inter-module dependencies

- Hardware and software configuration

- An example use case

- And a few frequently asked questions

Let's first begin with an overview of the module.

## **LPTMR Features**

Features of the low power timer, include:

•A 16-bit counter: This block can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter across all power modes, including the low-leakage modes.

•The LPTMR is reset only on global power on reset (POR) or low voltage detect (LVD), allowing it to be used as a time of day counter.

•The interrupt is generated asynchronously to the system clock and can be used to generate a wakeup from any low-power mode, including the low-leakage modes.

•The LPTMR has a configurable clock source.

Now, let's discuss on-chip interconnections and inter-module dependencies.

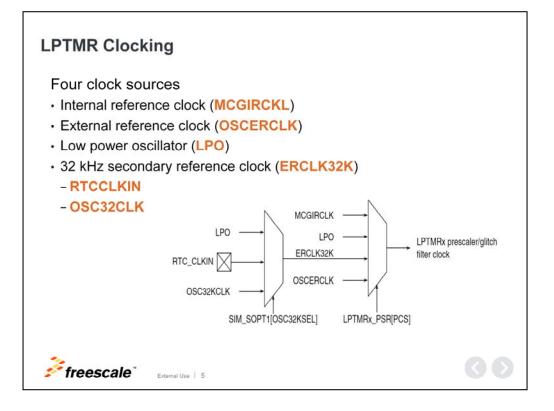

## LPTMR Clocking

There are four clock sources by which the LPTMR is clocked:

1. The internal reference clock. This reference is not available in VLPS, LLS or VLLS modes.

2. The external reference clock, which is not available in VLLS0 mode.

3. The low power oscillator. This is a 1kHz clock and is also not available in VLLS0 mode.

4. The 32 kHz secondary external reference clock, which is available in all low power modes.

The LPTMR operates in all power modes as long as a clock is available.

The LPTMR prescale register configures the input source to be used in pulse counter mode with the prescaler clock select bits. These bits should only be altered when the LPTMR is disabled.

Now, let's discuss hardware configuration.

| <ul> <li>- LPTMR_ALT3</li> <li>• CMP Counting</li> <li>- Counts CMP compared</li> </ul> | rison on CMP0 only           |                                  |

|-----------------------------------------------------------------------------------------|------------------------------|----------------------------------|

|                                                                                         |                              | Chip input                       |

| LPTMR_CSR[TPS]                                                                          | Pulse counter input number   |                                  |

| LPTMR_CSR[TPS]                                                                          | Pulse counter input number 0 | CMP0 output                      |

|                                                                                         | · ·                          | LPTMR_ALT1 pin                   |

| 00                                                                                      | 0                            | LPTMR_ALT1 pin<br>LPTMR_ALT2 pin |

| 00 01                                                                                   | 0 1                          | LPTMR_ALT1 pin                   |

# **LPTMR Pulse Counter Input Options**

In pulse counter mode, the selected input source directly clocks the counter and no other clock source is required.

The external inputs for pulse counting are LPTMR\_ALT1, LPTMR\_ALT2, and when available LPTMR\_ALT3.

The LPTMR can also count CMP comparisons on CMP0.

## **Board Level Routing Suggestions**

Ensure the LPTMR\_ALT1, LPTMR\_ALT2, or LPTMR\_ALT3 pins you want to count pulses on are not being used by another feature.

Note that LPTMR\_ALT1 is muxed with XTAL, and LPTMR\_ALT3 is muxed with RESET\_B on some devices, limiting the use of these signals as inputs.

Next, let's move on and discuss software configuration.

## LPTMR Register Setup

The LPTMR only has three configuration registers, so the setup for basic timer counting and pulse counting is straight forward.

The three configuration registers are:

- 1. The low power timer control status register

- 2. The low power timer prescale register

- 3. The low power timer compare register

Before using any of these registers, it is important to enable the clock gate to the LPTMR. In addition, any configuration to the LPTMR should happen with the timer disabled, with LPTMRx\_CSR[TEN]=0 and

always set LPTMRx\_CSR[TEN] to 1 as the very last step

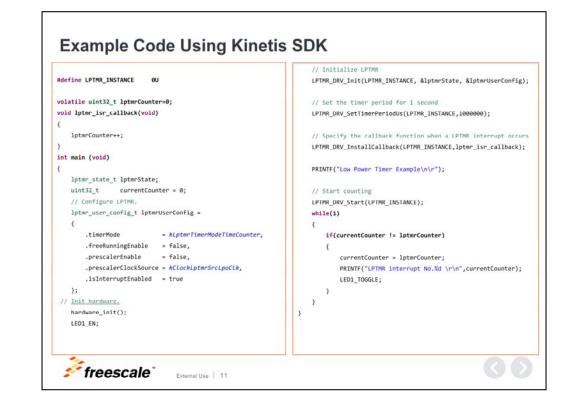

## **Example Code Using Kinetis SDK**

This is an example of the LPTMR configured to generate an interrupt every second. When the interrupt is triggered, LED1 changes status and information is printed to a terminal.

To initialize the LPTMR module, call the LPTMR\_DRV\_Init() function.

In order to use this function, it is necessary to define data structure lptmrUserConfig. This contains the LPTMR user configuration options.

In order to set the period, call the function LPTMR\_DRV\_SetTimerPeriodUs (microseconds). This function configures the LPTMR time period in microseconds, while the LPTMR is working as a time counter. After the time period, the callback function is called. This function cannot be called while the LPTMR is working as a pulse counter. The value in microseconds (us) should be an integer multiple of the clock source time slice.

If the interrupt is enabled, then it is necessary to use the LPTMR\_DRV\_InstallCallback function. This function installs the user-defined callback in the LPTMR module. When an LPTMR interrupt request is served, the callback is executed inside the ISR.

Let's review an example use case.

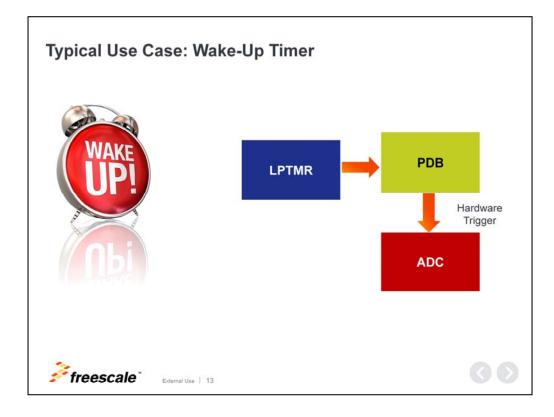

## Typical Use Case: Wake-Up Timer

The LPTMR is useful in low power applications. In this example, you'll see it is used as a wake-up timer to wake the part out of sleep modes after a certain amount of time.

If a clock is not available, the LPTMR can be used in pulse counter mode with the glitch filter enabled to wake-up the part based on pulse counts.

In addition the LPTMR can trigger events like an ADC conversion.

Now, let's review some frequently asked questions.

## LPTMR FAQs

#### Question: Does the LPTMR counter increment while in debug?

Answer: Yes, the LPTMR counter increments even while halted in debug.

#### Question: The reference manual mentions an LPTMR\_ALT3 input pin; where is it?

Answer: This input is chip dependent. Please refer to the pinout diagram in the reference manual to confirm whether it is available in your package.

#### Question: How do I properly read the counter register (LPTMRx\_CNR)?

Answer: The counter register (LPTMR\_CNR) cannot be initialized, but can be read at any time by ensuring that the bus clock is at least two times faster than the rate at which the LPTMR counter is incrementing and that on each read, the software first writes to the CNR with any value.

This concludes our presentation on the LPTMR module.

For more information on the LPTMR for Kinetis MCUs, please visit the references listed here.

We also invite you to visit us on the web at Freescale.com/Kinetis and check out our Kinetis community page.