# New QorlQ Generation: AMP Up Your Performance

# John Dixon

# Introduction

Freescale has been meeting the needs of thousands of customers with generations of PowerQUICC and QorlQ communications processors. As market conditions evolve, it has proved challenging to deliver the horsepower, lower power and easier-to-use tools that customers require with standard silicon manufacturing techniques. As a result of this, Freescale recently announced the next generation QorlQ Advanced Multiprocessing (AMP) series of processors, built on 28 nm process technology, which redefines levels of performance and power efficiency not previously attainable.

# Challenges Faced by Equipment Vendors

Moore's Law states that the number of transistors that can be placed inexpensively on an integrated circuit doubles approximately every two years. Today's network bandwidth challenges Moore's Law—traffic is doubling every 12 months as the demand for social media and rich content grow. The insatiable demand for connectivity will continue to push the industry for solutions that deliver performance beyond Moore's Law, with improved efficiency and lower operating costs.

# Freescale Power Architecture<sup>®</sup> Solutions

Freescale QorlQ communications platforms provide developers with a series of multicore processors based on high-performance Power Architecture® cores. These processors meet the through-put requirements for today's infrastructure applications that need robust real-time, point-to-point communication. QorlQ processors provide an evolutionary step up that preserves legacy investments in earlier generation PowerQUICC communications processors. The workhorse of the QorIQ P series is the P4080 processor with eight integrated e500mc cores, operating at frequencies up to 1.5 GHz, combined with high-

| Improvement of DMIPs Dual Thread Efficiency<br>Per Thread 2.4x                                                                                                         |                                                                                                                                                     | Frequency<br>1.3x                                          | Number of Cores 1.5x                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPC Improvements                                                                                                                                                       | Multi-threading                                                                                                                                     | Frequency Improvements                                     | Multicore                                                                                                                                                                                                                                                  |

| <ul> <li>64-bit architecture</li> <li>AltiVec Technology: 240 GFLOPS</li> <li>1TB physical address</li> <li>Accelerate Hypervisor performance<br/>with LRAT</li> </ul> | <ul> <li>Dual thread</li> <li>Each with separate front end, branch<br/>unit and LSU</li> <li>Larger amount of onboard cache<br/>per core</li> </ul> | New process and e6500 core<br>allowing increased frequency | <ul> <li>Up to 24 virtual cores</li> <li>Large 2 MB shared L2 cache within<br/>a cluster of one to four cores</li> <li>CoreNet cache-coherent fabric<br/>with multiple clusters to scale from<br/>one to eight clusters</li> <li>Virtualization</li> </ul> |

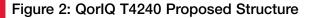

# Figure 1: New Advanced Multi-Threaded e6500 Core

## >4x performance improvement over previous generation

performance data path acceleration (DPAA) logic, and network and peripheral bus interfaces in a 45 nm implementation. Freescale's QorlQ AMP series is able to push its compute and energy performance envelope beyond the P4080 processor (Figure 1) such that its performance capacity exceeds that which Moore's Law predicts.

By taking advantage of multiple innovations that work together, QorIQ AMP series processors are able to improve software developer productivity while delivering a better than 4x improvement in application and core processing performance, and also deliver a better than 2x improvement in power efficiency (over the P4080 device). Key innovations that enable these improvements include advanced multi-threaded e6500 core, improvements in the high-performance memory, interconnects and applicationspecific accelerators, all implemented in a 28 nm process.

Energy efficiency is improved by better than 2x over the previous generation QorlQ devices through advanced power management such as the inclusion of cascading power management for core and system power management, special attention to multicore clustering optimizations and aggressive use of hardware acceleration.

## e6500 Core

The advanced multi-threaded e6500 core is based on a 64-bit architecture sporting large L1 caches and a 2x 2-way superscalar execution engine that can operate at up to 2 GHz, which is a 1.3x frequency improvement over the e500mc in the P4080.

Register settings allow developers to use 32-bit or 64-bit mode. A hybrid 32-bit mode supports e500 legacy software and supports a smooth transition to the 64-bit architecture. The e6500 core provides a dual-thread capability that enables each core to act as two virtual cores. Each thread has dedicated fetch. decode, issue and completion resources. Each thread also has a dedicated branch unit, load/ store unit (LSU) and simple fixed point execution units. The complex fixed point execution unit as well as the floating point unit and the AltiVec vector engine are shared between threads.

Each e6500 core is able to address up to 1 TB of memory space. The first product scheduled to be released in the QorlQ AMP series is the T4240 processor. This processor has 12 dualthreaded cores (24 virtual cores) where each dual-threaded e6500 core can be clustered in groups of four cores that share a common 2 MB L2 cache. The CoreNet cache-coherent fabric scales to support up to eight multiple clusters in a single system.

Optimizations in the memory architecture yield 2.4x improvement in the memory bandwidth and 1.6x improvement for the double data rate (DDR) clock frequency over previous generation QorlQ processors.

The e6500 core includes several features to support hardware-assisted virtualization, such as an extra privilege level for hypervisor support. Hardware support for logical to real address translation (LRAT) considerably reduces hypervisor overhead. A new logical partition ID field enables developers to identify partitions for virtual to real address translation. I/O MMU-like capabilities were added to the system to prevent data corruption for DMA or I/O. Network-bound interfaces are virtualized, and virtualization of hardware blocks is supported via the QMan for best-effort virtualization.

The e6500 core includes a 16 GFLOPS AltiVec execution unit that is able to improve the performance of algorithms such as the scheduler algorithm and media processing by a factor of four over a C-optimized implementation on the P4080. AltiVec technology is a vector or single instruction multiple data (SIMD) architecture that allows the simultaneous processing of multiple data items in parallel.

The QorlQ AMP series includes additional application-specific accelerators such as a security engine (SEC), DPAA, data flow acceleration, pattern matching engine (PME) and a hardware decompress/compress engine (DCE) that can dramatically improve network processing.

The QorlQ AMP processors push beyond a 2x improvement in power efficiency over previous generation QorlQ devices. Implementing the AMP processors in a 28 nm process yields 50 percent power savings. The cascading power management architecture enables reduced energy consumption under light network loads and automatically returns to full function when network loads increase. Developers are also able to dynamically set and change core operating frequencies for each cluster of cores.

The cascading power management architecture supports a state retention power gating (SRPG) "fast on, fast off" technique that allows the voltage supply to be reduced to zero for the majority of a block's logic gates while maintaining the supply for the state elements of that block to support fast wake up times. Because these processors do not have to save/restore processor state to memory, they have a greater than 10x improvement in their wake up response time.

QorlQ AMP processors build on the architecture powering existing QorlQ processors, and they maintain software code compatibility with the existing QorlQ P series, QorlQ Qonverge and PowerQUICC processors. On-chip, in-silicon debugging support includes deep inspection debug that provides visibility at the core, accelerator and fabric level of the processor. Full system trace includes change of flow, process and originator trace that is integrated with instrumented OS trace. A developer has complete control of event configuration to best be able to monitor, trigger, timestamp and count thousands of core/SoC events and user-defined messages. The debug architecture enables tracking core interactions with advanced cross-triggering. Built-in security mechanisms prevent debug interface intrusions. The debugging system also supports configurable black box recording for post-mortem debug. Development is supported by Freescale's CodeWarrior tools and VortiQa software, as well as third-party tools from Enea®, Green Hills®, Mentor Graphics, QNX<sup>®</sup> and Wind River<sup>®</sup>.

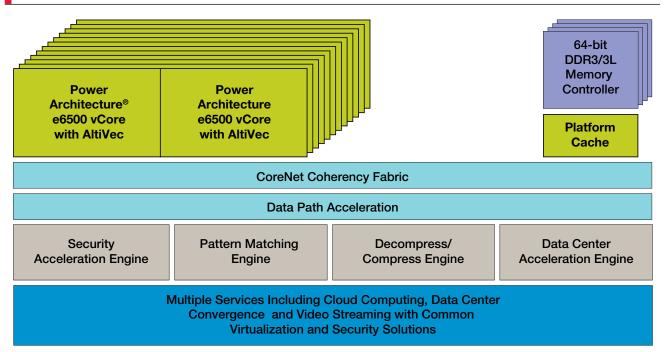

# QorlQ T4240 Processor

The QorlQ T4240 (Figure 2) is the first AMP series device scheduled for release in 2012 and targets data center networking, metro carrier edge/core routers, aerospace and defense, as well as access gateway applications. Additional AMP devices are planned for release each quarter thereafter. The T4240 processor integrates twelve e6500 cores in a single device that are organized into three processor clusters of four cores each. The 24 virtual cores are able to operate at up to 1.8 GHz and support processing for 48 Gbps packet throughput.

System performance for the QorlQ AMP T4240 processor is rated at up to 4x better than the CPU performance of the previous generation eight-core P4080 device. The L2 cache is six times larger. The T4240 processor delivers 3x better acceleration for data path acceleration and 2x better throughput for the CoreNet fabric, security engine, OCEAN and data flow acceleration blocks. New functions of data decompression/ compression accelerator (20 Gb per second), Interlaken Look-Aside (80 Gb per second), PCIe 3.0, SR-IOV end point and data center bridging are not available on the P4080 and are new with the T4240 processor.

# Conclusion

Smaller process implementations demonstrate that technology scaling continues to deliver benefits. At 28 nm, QorlQ processors experience 50 percent lower power to retain constant processing performance while enjoying a 40 percent silicon area reduction over 45 nm implementations. Freescale's experience with 28 nm process technology continues to suggest that next-generation application performance will be achieved through a combination of smaller process nodes and the use of more processing engines—in the form of more cores and accelerators. This combination is expected to deliver up to 4x improvement in application performance at the new process node, exceeding the limitation of Moore's Law and helping to enable a more connected world.

# How to Reach Us:

### Home Page:

freescale.com

# Power Architecture

Portfolio Information: freescale.com/power

e-mail: support@freescale.com

### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 1-800-521-6274 480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 303-675-2140 Fax: 303-675 2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright license granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

### For more information, visit freescale.com/power

Freescale, the Freescale logo, AltiVec, CodeWarrior, PowerQUICC and QorIQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. QorIQ Oonverge and VortiQa are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Document Number: PWRARBYNDBITSQIG REV 0